基于可編程展頻時鐘生成器的降低EMI干擾技術介紹

本文引用地址:http://www.czjhyjcfj.com/article/190640.htm

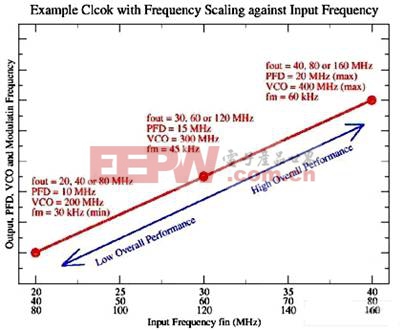

圖5:GP SSCG緩沖器芯片中的頻率調整。

當實際配置和這些理想設置有偏差時,各種副作用就會產生。比如,如果輸入頻率不在所選范圍的正中,VCO和調制頻率就會被直線調整(下圖6)。

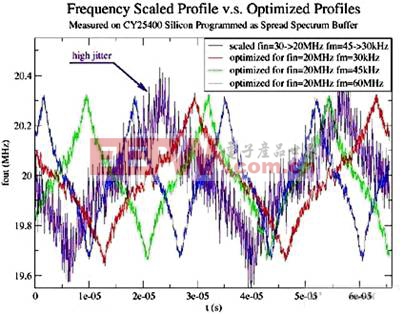

如果PLL帶寬太低(一般是由于控制周期間抖動,如圖6所示),那么頻率概圖就會變形,從而影響EMI性能。

當輸入頻率最低時,結果是最糟糕的:因為PDF和VCO頻率都很低,周期間抖動大大增加,并且由于調制頻率低而頻率概圖可能變形,EMI抑制性能就會大大降低。

圖6:頻率調整和理想概圖比較。

當擴展量的選擇受到限制時,開發人員就必須選擇一個超出需要的更大擴展量。這常常會增加周期間抖動,并降低系統時序預算。

如果沒有一個擴展率可以滿足系統要求,開發人員就必須要求時鐘供應商對設計作出改動并提供一款新的芯片,而這個過程中,哪怕僅僅是改變一個金屬層那么簡單,也最少需要數周的時間,并且成本一般都非常高。

與之相比,一個可編程的展頻時鐘生成器則能夠提供支持可現場編程性的通用時鐘,并結合片上非易失性存儲器,實現動態的展頻參數重置,從而不需要讓廠家花大量時間和成本對芯片進行改動。

可編程性還讓展頻時鐘性能能夠針對所要求的規格進行優化。比如,開發人員可以規定2.1%的精確擴展率(而不是固定選擇的3%),或者為實現所需的頻率設置而優化調制模式。

上面的圖4展示了如何利用一個帶有2個展頻PLL的4PLL型時鐘芯片,通過調制頻率優化來輕松將EMI降低3 ~4 dB的。這些擴展的PLL都有兩個獨立擴展模式可供選擇。

大部分開發人員都更喜歡使用Hershey Kiss展頻時鐘來實現更好的EMI抑制性能,但很多時鐘供應商都只提供線性展頻時鐘。在理想情況下,一個SSCG必須同時提供Hershey Kiss和線性展頻時鐘。圖3展示出Hershey Kiss展頻時鐘在上面所示的4PLL時鐘芯片測試條件下一次性EMI降低了1.67dB。

另外,重要的時鐘參數,例如PLL電荷泵電流、VCO增益和輸出驅動強度,都是必須能夠編程設置的。這樣的靈活性能夠大大提高系統性能,減少系統開發時間,將改動限制到最小并降低風險。

評論