基于FPGA的星載計算機自檢EDAC電路設計

在本設計中,我們采用外置的CPU芯片和內置的RAM單元,作為自檢EDAC電路的硬件平臺 (或環境、資源)。CPU芯片在這里起到的作用是啟動EDAC自檢,處理錯誤中斷,向地面傳 送錯誤信息,并根據地面要求對錯誤信息進行處理。

在該設計中,檢測一個存儲單元地址僅需要4個時鐘周期,如果開啟自糾錯功能,并且 檢測到單比特錯誤,再增加2個時鐘周期用來糾錯。因此如果時鐘為20MHz,并且錯誤數據較 少,則更新1M個RAM存儲單元需要的時間約為:4×1M 20MHz = 0.2s。

更重要的是,在這0.2s的時間里,僅在出現錯誤時需要向計算機產生中斷,進行相應處 理,對地面進行錯誤報告,因而CPU處理時間很短,節省了寶貴的CPU資源。

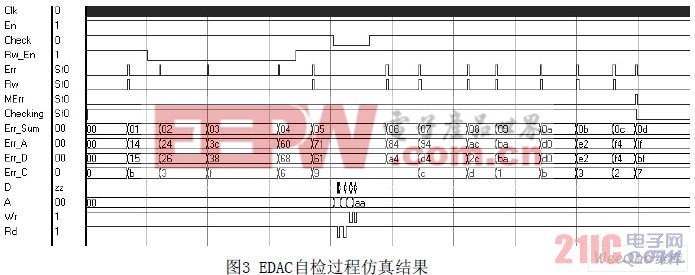

3.3 仿真與驗證

在空間環境下普遍存在的SEU,在地面環境下是很難獲得的,為了在地面對該EDAC電路 設計進行驗證,需要采取故障注入手段。由于在本例中RAM存儲單元采用FPGA內部資源,因 此故障注入變得相對簡單。在FPGA進行程序綜合時,可將預先編制好的RAM存儲單元初始化 文件一起綜合。因此我們可在編制RAM存儲單元初始化文件時,對某些比特位進行修改,以 模擬空間環境下SEU對RAM存儲單元的影響。

在這里采用Xilinx公司的XQRV300為硬件載體,該型號FPGA芯片在航天領域內被廣泛使 用。為節省仿真時間,數據RAM存儲單元采用256*8bit,檢驗RAM存儲單元采用25*bit。在 RAM存儲單元初始化文件中,人工加入了12個單比特錯誤,以及1個兩比特錯誤,如下表所示。

為仿真簡便起見,向存儲單元存放的正確數據與存儲單元地址相同。

時鐘選擇為20MHz,通過采用ModelSim軟件進行布線后仿真,我們可以得到圖3所示結果。

圖中: Clk — 系統時鐘;

En — EDAC 模塊使能控制;

Check — 自檢啟動/使能信號(信號上升沿觸發一次巡檢,信號為低暫停巡檢);

Rw_En — 自糾錯使能信號(為高允許糾錯);

Err — 錯誤中斷(標志)信號;

Rw — 自糾錯標志信號(為高表示正在進行自糾錯操作);

MErr — 多比特錯誤中斷(標志)信號;

Checking — 自檢標志(為高表示尚未完成本次巡檢操作);

Err_Sum,Err_A,Err_D,Err_C — 錯誤計數,錯誤地址,原始數據,原始校驗碼;

D,A,Wr,Rd — 單片機數據、地址、寫操作、讀操作信號;

評論