快速實現SHA-1算法的硬件結構

實現結果

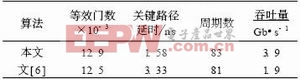

使用Verilog硬件描述語言按本文提出的優化方法實現了SHA-1算法,并使用Synopsys Design Compiler在0.18Lm標準單元庫下綜合,得到表1中的結果。表1中還包括了文[6]的實現結果。文[6]同樣使用了0.18Lm工藝,但是實現SHA-1算法的方法仍然是傳統的直接計算ABCDE5個中間變量的方法。

表1 ASIC實現結果比較

從前文的算法分析可以看出,傳統實現方法的關鍵路徑上有4次加法,如果把這4次加法按樹型組織,那么關鍵路徑的延時大約為3個32bit加法器的延時;通過本文方法改進后,關鍵路徑延時可以縮短為1個32bit加法器延時加上少量組合邏輯延時。因此理論上速度大約可以提高為傳統方法的2~3倍。從表1和使用傳統方法實現的文[6]對比可以發現,實現結果和理論分析完全一致。改進方法因為計算中引入了中間變量,所以面積比傳統方法要略大;同時為了計算中間變量的初值,每塊數據也需要多兩個周期的計算。但是因為關鍵路徑得以明顯縮短,整體的計算速度大大提高,吞吐量達到傳統方法的兩倍以上。

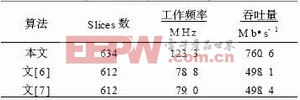

通過縮短關鍵路徑加速SHA-1計算的方法不僅適用于ASIC設計,而且一樣適用于基于FPGA的硬件設計。文[6,7]是目前常用的兩種SHA-1算法的商業IP核。使用本文提出的改進方法在和文[6,7]同樣的FPGA芯片上(XilinxVirtex2II系列XC2V50025)實現SHA-1算法。具體結果以及和文[6,7]結果的對比見表2。

表2 FPGA實現結果比較

結論

針對有理分式擬合中的保證生成二端口網絡無源性的問題,本文提出了一種簡單且有效的局部補償方法,其主要思想在于:在生成網絡的Y參數矩陣的對角元素上加上(相當于并聯)一個RLC串聯的濾波回路,使得該回路可以以恰好補償原網絡違反無源性條件的頻率段,而盡量少的引入誤差。經過實驗表明,該方法能很好的達到預期的目的,在保證無源性條件的同時,能使引入的誤差限制在2%以內。

評論