基于FPGA的應力應變信號監測系統的研究設計

4.3 D/A轉換器0832控制模塊

FPGA控制DA芯片,使DAC0832的輸出與ADC芯片MAX197的輸入模擬電壓相加,抵消輸入的零點,產生0—4.096V有效輸出送到ADC芯片MAX197輸入端進行模數轉換,控制模塊如圖6所示。本文引用地址:http://www.czjhyjcfj.com/article/189659.htm

4.4 雙端口異步FIFO緩存模塊

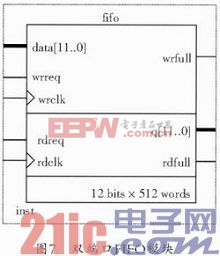

由于軟核處理器和FIFO的時鐘不同,處理器讀速度遠遠大于FPGA采集數據的速度,因此設計用FIFO在處理器和FPGA間的跨時鐘域數據傳輸中起緩存的作用。在Quartus II9.0中用Altera提供的免費FIFO核設計生成的FIFO緩存模塊如圖7所示。

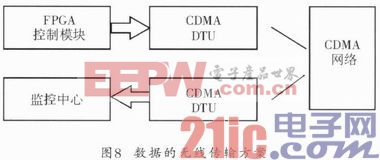

5 數據傳輸模塊設計

數據是通過無線的方式進行數據傳輸如圖8所示,通過CDMA網絡傳輸,工作量小,且方便維護,成本也低,可以通過CDMA網絡實現數據的實時傳輸。

監控中心采用查詢方式接收/發送數據,數字信號處理模塊采用中斷方式接收數據。查詢方式發送數據。在監控中心向數字信號處理模塊發送數據時,先把數據發送到管理模塊,管理模塊再將數據發送到數字信號處理模塊,當數據發送結束時,比較數字信號處理模塊的模塊編號和監控中心發送的模塊編號是否匹配,如果匹配則接收數據并存入數據庫,并實時顯示,監控中心的數據顯示模塊主要顯示監測點,以及對應的應變值、溫度值和應變、溫度的最大值和最小值。并將數據保存起來然后通過對數據的分析處理,對系統的結構安全狀況做出評估。

6 結束語

本設計將FPGA (現場可編程門陣列)引入應力應變檢測系統的設計。FPGA的時鐘頻率高、內部延時小、以FPGA內部的強大邏輯功能代替復雜的外圍電路來控制數據采集模塊組,既保證了數據采集模塊實時、同步采樣,又簡化了硬件電路,增強了系統的抗干擾能力,具有很高的實用價值。

fpga相關文章:fpga是什么

評論