基于FPGA的AVS視頻解碼芯片仿真和驗(yàn)證平臺(tái)設(shè)計(jì)

1.1.2 視頻解碼軟件實(shí)現(xiàn)

在完成系統(tǒng)的硬件設(shè)計(jì)后, 利用Altera提供的Nios II IDE軟件,實(shí)現(xiàn)應(yīng)用程序的軟件設(shè)計(jì),主要是CPU控制主程序以及能夠獨(dú)立完成視頻解碼的軟件程序。將待驗(yàn)證的硬件模塊掛接到Avalon總線(xiàn)上,此時(shí)FPGA中既放入解碼系統(tǒng)的硬件模塊,也放入了解碼系統(tǒng)的軟件模塊,RISC CPU 完成PC機(jī)上CPU的功能,控制系統(tǒng)軟硬件模塊的運(yùn)行。待解碼的AVS視頻碼流通過(guò)USB接口送給驗(yàn)證平臺(tái)上的視頻解碼系統(tǒng),RISC CPU協(xié)調(diào)放在FPGA中的AVS解碼系統(tǒng)硬件模塊和軟件模塊以完成解碼。AVS數(shù)據(jù)經(jīng)過(guò)解碼,轉(zhuǎn)換成可以播放的YUV格式的視頻數(shù)據(jù)。

1.2 VGA顯示設(shè)計(jì)

該部分將上述視頻解碼軟件轉(zhuǎn)換成的YUV數(shù)據(jù)經(jīng)過(guò)視頻控制器做一些后處理和視頻格式轉(zhuǎn)換的工作,然后將YUV視頻數(shù)據(jù)通過(guò)VGA控制接口,最后在VGA顯示器上將這些視頻信號(hào)顯示出來(lái)。下面分別介紹該部分的硬件開(kāi)發(fā)設(shè)計(jì)和軟件程序?qū)崿F(xiàn)。

1.2.1 VGA顯示硬件設(shè)計(jì)

在該設(shè)計(jì)中,Nios II軟核處理器主要完成CFI-Flash和SDRAM存儲(chǔ)器的讀寫(xiě)操作,并且控制VGA的顯示。在SoPC Builder中搭建VGA顯示部分的硬件系統(tǒng)。針對(duì)系統(tǒng)的要求,在FPGA外圍連接了SRAM、SDRAM和Flash等存儲(chǔ)器,它們可以滿(mǎn)足視頻處理過(guò)程中對(duì)于存儲(chǔ)器的不同要求。其中,SRAM作為CPU控制主程序運(yùn)行的內(nèi)存;Flash用于存儲(chǔ)播放的YUV視頻文件;SDRAM容量大、速度快,用于VGA顯示的緩存,確保視頻播放的流暢。并沒(méi)有直接將SDRAM掛接到Avalon總線(xiàn)上,而是自己編寫(xiě)了SDRAM端口控制器,再將其掛接到Avalon總線(xiàn)上,通過(guò)端口控制器對(duì)SDRAM進(jìn)行讀寫(xiě)操作。

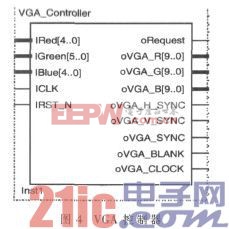

視頻文件從Flash寫(xiě)到SDRAM后,再經(jīng)過(guò)VGA控制器顯示到顯示器上。VGA控制器采用Verilog語(yǔ)言編寫(xiě),使其具有更高執(zhí)行性能,如圖4所示。

1.2.2 VGA顯示軟件設(shè)計(jì)

在Nios II軟件開(kāi)發(fā)過(guò)程中,使用Altera提供的IO操作函數(shù)對(duì)SDRAM進(jìn)行寫(xiě)操作,并且利用Altera提供的API函數(shù)對(duì)Flash進(jìn)行讀操作。具體函數(shù)如下:

Alt_flash_fd * fd

fd = alt_flash_open_dev(/dev/cfi_flash);

alt_read_flash(fd, CFI_FLASH_BASE+202752*j, buf, 202752);

for(i=0; i101376;i++)

{ IOWR_16DIRECT (SDRAM_0_BASE, 0, buf[i]);

2 驗(yàn)證實(shí)例

基于提出的AVS視頻解碼芯片驗(yàn)證框架,實(shí)現(xiàn)了基于FPGA的AVS解碼芯片驗(yàn)證平臺(tái),驗(yàn)證平臺(tái)分為視頻解碼系統(tǒng)和VGA顯示系統(tǒng)兩部分。視頻解碼系統(tǒng)可以嵌入待驗(yàn)證的硬件模塊或下載待驗(yàn)證的視頻解碼器。基于該解碼芯片驗(yàn)證平臺(tái),完成了AVS解碼芯片以及其中幀內(nèi)預(yù)測(cè)、熵解碼和環(huán)路濾波等主要硬件模塊的驗(yàn)證。相對(duì)于Modelsim的軟件仿真,硬件驗(yàn)證平臺(tái)大大提高了驗(yàn)證速度,同時(shí)也為成功投片提供了可靠保障。圖5為驗(yàn)證平臺(tái)中視頻解碼系統(tǒng)的軟硬件解碼過(guò)程。

在硬件系統(tǒng)設(shè)計(jì)過(guò)程中,F(xiàn)PGA驗(yàn)證已成為了系統(tǒng)設(shè)計(jì)的重要一環(huán)。本文提出了視頻解碼芯片的驗(yàn)證框架,并設(shè)計(jì)實(shí)現(xiàn)了基于FPGA的視頻解碼芯片驗(yàn)證平臺(tái)。該硬件驗(yàn)證平臺(tái)包括視頻解碼系統(tǒng)和VGA顯示系統(tǒng)兩部分,通過(guò)視頻解碼系統(tǒng)可以嵌入待驗(yàn)證的視頻解碼系統(tǒng)和硬件模塊,提高了驗(yàn)證速度和效率。該驗(yàn)證平臺(tái)具有操作靈活、驗(yàn)證效率高、可重用性強(qiáng)和易擴(kuò)展為驗(yàn)證其他視頻標(biāo)準(zhǔn)解碼芯片的驗(yàn)證平臺(tái)等優(yōu)點(diǎn)。基于該驗(yàn)證平臺(tái)已實(shí)現(xiàn)了多個(gè)硬件模塊和AVS視頻解碼芯片的驗(yàn)證。

fpga相關(guān)文章:fpga是什么

pic相關(guān)文章:pic是什么

評(píng)論