基于FPGA的DDR2 SDRAM存儲器用戶接口設計

接口控制模塊主要是接收寫通路的寫操作請求信號以及它對應的地址信號和數據信號,讀通路的讀操作請求信號以及它對應的地址信號,并將這些信號按照DDR2存儲控制器的時序要求發送給DDR2存儲控制器,之后再接收DDR2存儲控制器發回的讀數據。DDR2存儲控制器的讀寫操作時序如圖3所示。本文引用地址:http://www.czjhyjcfj.com/article/189601.htm

3 仿真驗證

對本設計的驗證采用的是6路8位數據以27 MHz的頻率寫入讀出操作。對其進行整體讀寫仿真的時序結果如圖4所示。

由該圖可知,當將數據寫入到DDR2中的數量到達一定程度時,開始向向外讀出數據,寫入的時序和讀出的時序整體上符合設計要求。

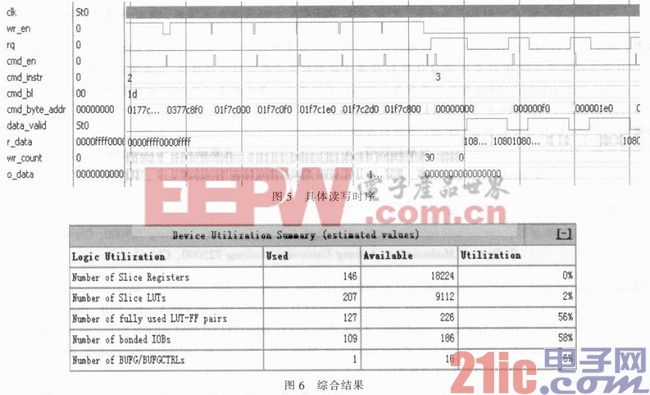

對讀寫操作的具體仿真時序如圖5所示。

由該圖可知,寫操作時的各種控制指令以及地址和數據的發送都是完全正確的;讀操作時的各種控制指令以及地址和數據的發送也是完全正確的。

對該設計采用XILINX Spartan6系列的xc6slx16—2ftg256器件進行綜合,其結果如圖6所示。

由該圖可知該設計使用的邏輯資源相當小,其中寄存器還不到總數的百分之一,查找表也只使用了總數的百分之二。

4 改進

在一般情況下,DDR2的硬件存儲速率很快,其會等待存儲控制器發送下一個操作指令,而DDR2存儲控制器的操作指令是由用戶接口發出的,因此可以提出以下改進方案。可以在存儲控制器前端添加多個FIFO,將與操作有關的所有指令、地址以及數據對應起來存入這些FIFO中,這樣等到DDR2存儲控制器將本次操作完成之后自動將所有FIFO中與下次操作有關的指令和數據讀出,直接進行下一次DDR2的操作,與此同時用戶接口部分在這些FIFO沒滿的情況下,還仍然向這些FIFO中寫入要操作的所有指令和數據。

5 結論

由以上仿真結果可知,該設計在整個設計讀寫頻率很高時仍然可以保證所有數據的正確操作,不會存在數據的丟失或者錯誤。由以上綜合結果可知,該設計占用的FPGA片上資源很少,運行頻率很高,基本可以滿足所有設計的要求。因此可知,該設計具有很高的工作頻率,解決了電路設計中DDR2存儲器讀寫操作頻率的瓶頸問題,使得整個設計的工作效率得到很大的提高。

fpga相關文章:fpga是什么

存儲器相關文章:存儲器原理

評論