基于CS5321與CS5322的多路數(shù)據(jù)采集系統(tǒng)

∑一△A/D轉(zhuǎn)換技術(shù)以其高分辨率和大的動(dòng)態(tài)范圍在數(shù)據(jù)采集系統(tǒng)中得到了廣泛應(yīng)用:但∑一△A/D轉(zhuǎn)換器通常采用串行傳輸,因此由它實(shí)現(xiàn)的采集系統(tǒng)大多包含串并轉(zhuǎn)換單元。為了達(dá)到系統(tǒng)設(shè)計(jì)簡(jiǎn)化,降低系統(tǒng)成本的目的,探討一種直接用串行傳輸?shù)亩嗤ǖ?a class="contentlabel" href="http://www.czjhyjcfj.com/news/listbylabel/label/數(shù)據(jù)采集系統(tǒng)">數(shù)據(jù)采集系統(tǒng)的方法十分有必要。

采用∑一△A/D有三個(gè)優(yōu)點(diǎn):第一是∑一△A/D轉(zhuǎn)換器的前端無(wú)需設(shè)置大陡度的抗混疊模擬濾波器,也無(wú)需設(shè)置采樣保持電路;其次,由于∑一△A/D可直接對(duì)大動(dòng)態(tài)范圍的模擬信號(hào)進(jìn)行高精度的轉(zhuǎn)換,無(wú)需加上程控放大器;最后,由于∑一△A/D一般都采用串行方式進(jìn)行數(shù)據(jù)傳輸,如果系統(tǒng)設(shè)計(jì)得當(dāng)?shù)脑挘涌陔娐穼?huì)非常簡(jiǎn)潔。

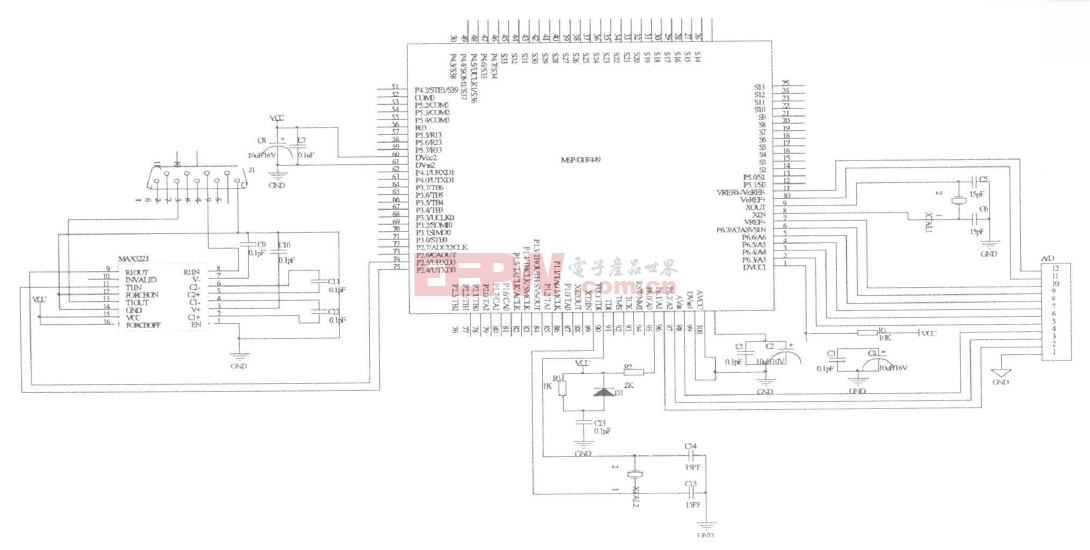

CS5321和CS5322分別是∑一△調(diào)制器和可編程多級(jí)FIR線性相位數(shù)字抽取濾波器。二者結(jié)合,可得到24位高精度A/D轉(zhuǎn)換器系統(tǒng),它們的接口電路如圖1所示。CS532

根據(jù)CS5321和CS5322的這些特點(diǎn),在選擇系統(tǒng)的中央處理及控制單元的時(shí)候,最好選擇字長(zhǎng)為32位的帶有串行口的DSP或其他的微處理器。

1 系統(tǒng)的總體接口

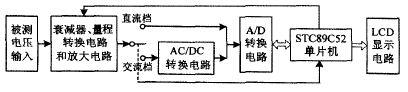

基于以上介紹及整個(gè)系統(tǒng)采用串行傳輸?shù)目紤],采集系統(tǒng)的總體接口框圖如圖2所示。

由圖1可見,多通道模擬信號(hào)先經(jīng)過前置放大器送到各自的∑一△A/D轉(zhuǎn)換器,得到的多通道數(shù)字信號(hào)在多路控制電路的作用下,通過串行口傳輸?shù)街醒胩幚砜刂茊卧?jīng)過適當(dāng)?shù)奶幚砗罂梢运腿氪鎯?chǔ)器中存儲(chǔ)。整個(gè)系統(tǒng)設(shè)計(jì)的關(guān)鍵在于多通道的串行口接口設(shè)計(jì),下面予以介紹。

2 多通道串行接口的設(shè)計(jì)原理與實(shí)現(xiàn)

由前面介紹可知,CS5322輸出為24位串行比特流,只需要加入少量的多路控制邏輯,就能夠?qū)崿F(xiàn)多通道的A/D轉(zhuǎn)換器與DSP的直接連接,幾乎不需要加入其他的任何接口邏輯電路。下面從分析∑一△A/D轉(zhuǎn)換器的工作時(shí)序開始,詳細(xì)介紹該采集系統(tǒng)的原理及具體實(shí)現(xiàn)。

2.1 ∑一△A/D轉(zhuǎn)換器的串口讀操作時(shí)序

由CS5321/CS5322組成的∑一△A/D轉(zhuǎn)換器的串行口讀操作時(shí)序如圖3所示。

當(dāng)CS5321/CS5322的輸入時(shí)鐘(CLKIN)為1 MHz時(shí),調(diào)制器(CS5321)輸出速率為256 Kb/s的串行抽樣比特流。通過對(duì)CS5322的抽取率控制位(DECC、DECB、DECA)的不同賦值,可以產(chǎn)生7種不同的輸出字率(即采樣頻率),字長(zhǎng)為24位。CS5322的初始化可以通過軟件編程,也可以通過硬件直接置位完成。具體采用哪種方法,可以根據(jù)系統(tǒng)的需要來(lái)選擇。

CS5322 的 DRDY為數(shù)據(jù)準(zhǔn)備好信號(hào)引腳。當(dāng)DRDY為高電平時(shí),表示CS5321/CS5322組成的∑一△A/D轉(zhuǎn)換器已經(jīng)進(jìn)行完一次轉(zhuǎn)換,并已由CS5322將數(shù)據(jù)在其輸出緩沖器中準(zhǔn)備好,數(shù)據(jù)可以從串行口輸出。CS5322中讀操作控制插針有CS、R/W、SCLK、SOD。當(dāng)CS=O且R/W=1時(shí),串行口處于讀操作有效。RSEL引腳用來(lái)選擇串口輸出的是數(shù)據(jù)緩沖器,還是狀態(tài)緩沖器的數(shù)據(jù),SOD為串行數(shù)據(jù)輸出插針。當(dāng)讀狀態(tài)被選擇后,不管SCLK是高電平還是低電平,第一位輸出數(shù)據(jù)都會(huì)在SOD插針出現(xiàn),并且在SCLK的下降沿終止。第一個(gè)SCLK下降沿后,每一個(gè)SCLK的上升沿從SOD引腳輸出一位數(shù)據(jù)。輸出的位流順序?yàn)楦呶?MSB)在前低位(LSB)在后。

2.2 多通道串行接口的原理

通過以上對(duì)CS5322的串行讀操作時(shí)序的分析,可以得到利用CS5321/CS5322實(shí)現(xiàn)的多通道數(shù)據(jù)采集系統(tǒng)的傳統(tǒng)方案。以M通道為例,系統(tǒng)的框圖如圖4所示。

在由CS5321/CS5322組成的∑一△A/D轉(zhuǎn)換器的多通道采集系統(tǒng)中,傳統(tǒng)方案如圖4所示。通過控制器輪流接通各道的DRDY信號(hào),在DRDY為高電平時(shí)各道輪流從SOD引腳將數(shù)據(jù)輸出到控制器。由CS5321/CS5322所組成的∑一△A/D轉(zhuǎn)換器的采樣率,由DECC、DECB、DECA三位設(shè)定,可以為62.5 Hz~4 kHz等7種。對(duì)應(yīng)每一種采樣率,所要求的移位時(shí)鐘(SCLK)的最低頻率fmin=fs

評(píng)論