拉普拉斯算子的FPGA實現方法

圖2(b)中的行緩沖器分別是由256個8位移位寄存器構成的寄存器鏈。當圖像的第N行數據在像素時鐘同步下輸入到行緩沖器1后,隨著第N+1行圖像數據輸入到行緩沖器2中,第N行的圖像數據依次存入,而當第N+2行圖像數據存入行緩沖器1后,行緩沖器2和行緩沖器3中分別存放的是第N+1行和第N行的圖像數據,從而實現緩沖圖像數據的功能。這樣在像素時鐘的同步下,第N,N+1,N+2行的同一列數據分別從taps0x,taps1x,taps2x端輸出,為構造3×3模塊提供了數據準備。本文引用地址:http://www.czjhyjcfj.com/article/188608.htm

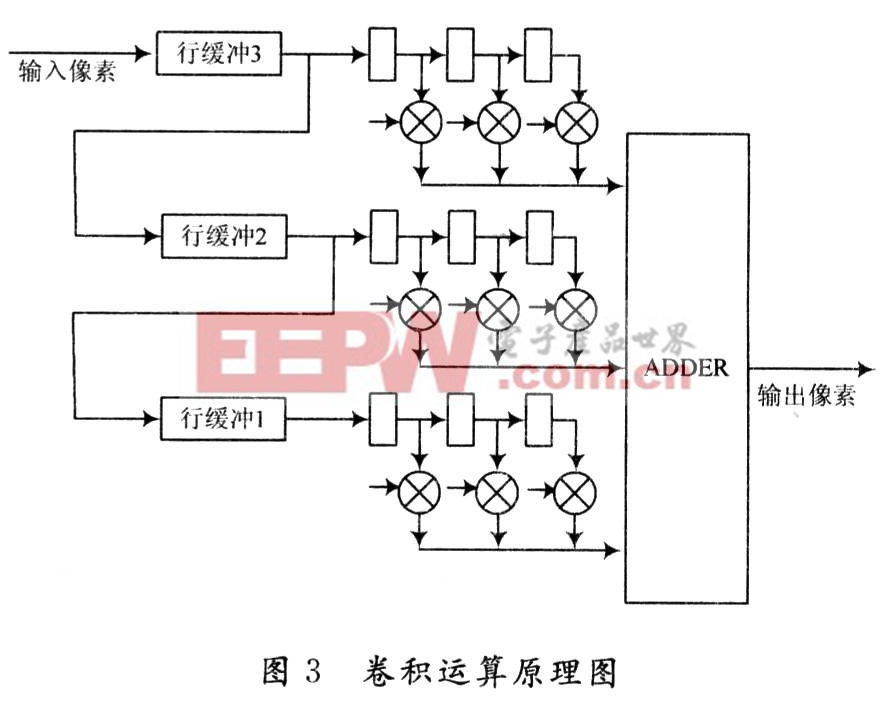

2.2 卷積計算模塊

圖3是3×3圖像卷積運算的原理圖。可以看出,為了實現卷積運算需要做乘法和加法運算,如果直接采用分立的D觸發器和加法器以及乘法器來完成卷積運算,結構會很復雜。在此,采用宏功能模塊中的可編程乘加器模塊和可編程多路并行加法器模塊Parallel_add實現卷積運算,大大簡化了設計。

使用可編程多路并行加法器Parallel_add宏功能模塊時,可以自由設計輸入數據位寬,累加數據個數,定義累加輸入數據類型,定義時鐘控制端口,增加異步清零端口等,能快速便捷地生成所需的加法器模塊。為了實現卷積運算中的加權和運算,宏功能模塊生成的3個乘加器,每個乘加器包含3個乘法器和1個加法器,如圖4所示。圖像數據從dataa依次輸入,數據分別與固定的模板系數datab_0,datab_1,datab_2相乘。在該實驗中,使用Verilog HDL語言為各datab設值,各值分別對應模板中的權值,并將結果送給加法器完成加法運算。

當采用3個這樣類似的Altmult_add模塊并聯時,便可實現Laplacian算子的運算。

完成圖像卷積后需要對結果進行處理,以防止結果出現負值或超過255范圍。使用QuartusⅡ提供的Lpm_abs宏功能模塊計算絕對值,可以解決出現負值問題,而對超過255的值則均設定為255。

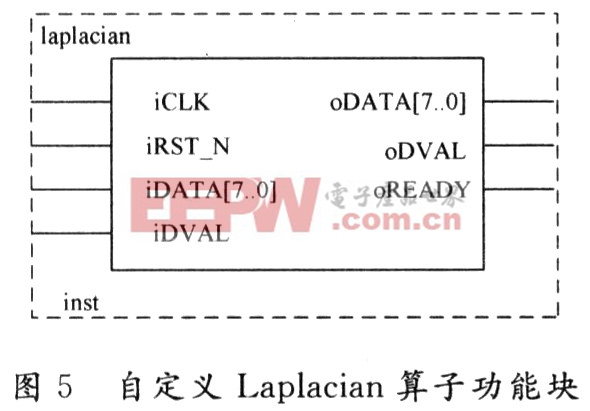

另外,自定義模塊如圖5所示,將它存于自定義宏功能庫中,在以后的設計時,只需修改相關參數即可方便的調用。

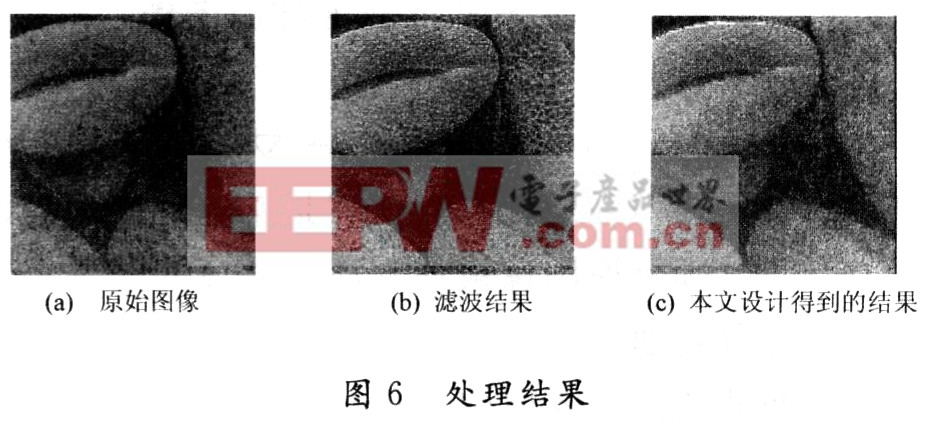

2.3 實驗結果

圖6(a)為一幅256×256的原始圖像,(b)為采用Matlab的Laplacian算子進行濾波的結果,(c)為采用本文設計的Laplacian算子得到的結果。比較圖6(b)和(c)可以看出,該硬件算法取得了較好的效果。

3 結 語

這里利用QuartusⅡ軟件提供的宏功能模塊,通過配置調用的宏功能模塊來實現Laplacian算子,該方法既避免了自己編寫大量程序代碼的繁瑣,又獲得較好的實現結果。最后通過與Matlab仿真結果相比較,證明了該設計的有效性。該設計方法方便、快捷,可以推廣到其他類型的模板設計中。

電源濾波器相關文章:電源濾波器原理

高通濾波器相關文章:高通濾波器原理

評論