基于AD7543和FPGA的數(shù)/模轉(zhuǎn)換電路設(shè)計(jì)

1.3 數(shù)/模轉(zhuǎn)換芯片AD7543器件工作原理

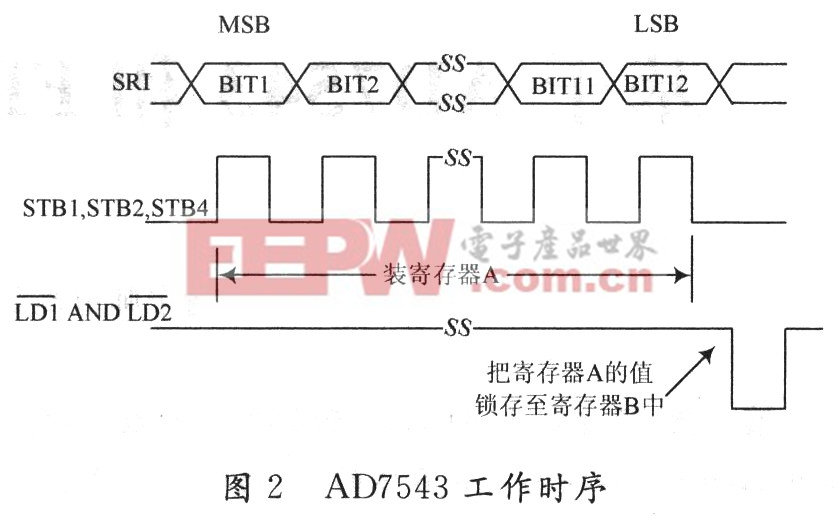

在AD7543器件內(nèi)部,有兩個(gè)寄存器:寄存器A和寄存器B。寄存器A是12位串行輸入并行輸出的移位寄存器,其低位與SRI引腳相連。在STB1,STB2和STB4上升沿或STB3下沿作用下,移位寄存器A發(fā)生移位,SRI引腳上的串行數(shù)據(jù)被裝進(jìn)寄存器A中,當(dāng)要寫(xiě)入數(shù)據(jù)全部被裝進(jìn)寄存器A時(shí),再給AD7543一個(gè)裝載負(fù)脈沖(LD1和LD2均為低電平),把移位寄存器A的內(nèi)容裝到寄存器B中,通過(guò)后續(xù)電路完成D/A轉(zhuǎn)換。當(dāng)CLR為低電平時(shí),寄存器B的數(shù)據(jù)被清零,輸出的電壓為零,簡(jiǎn)化初始化過(guò)程。圖2為AD7543數(shù)/模轉(zhuǎn)換(D/A)的工作時(shí)序圖。

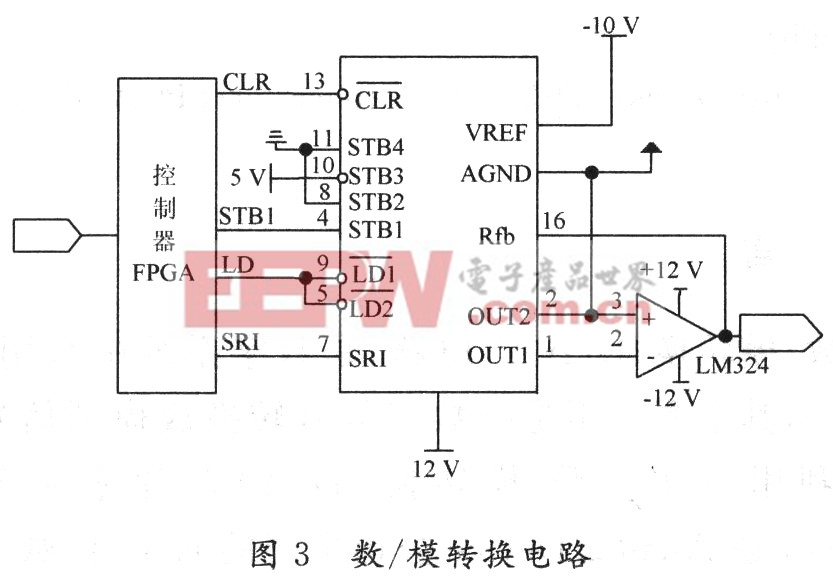

2 基于AD7543的數(shù)/模轉(zhuǎn)換器電路設(shè)計(jì)

圖3為基于AD7543數(shù)/模轉(zhuǎn)換芯片的數(shù)/模轉(zhuǎn)換器電路,由于AD7543的內(nèi)部無(wú)運(yùn)算大器,輸出為電流形式,在應(yīng)用中,必須外接一個(gè)運(yùn)放器,因此,AD7543的第1和2腳分別接在LM324運(yùn)放的反向輸入口與同相輸入口,AD7543的第15腳(參考電壓輸入端)接在-10 V的電源上,當(dāng)寄存器B的位數(shù)全為高電平時(shí),輸出電平接近10 V。AD7543的輸入時(shí)序信號(hào)CLR,STB2,LD和SRI由外接的可編程邏輯器件(FPGA)產(chǎn)生。AD7543的第8腳和11腳接地。運(yùn)放器LM324正負(fù)電源引腳分別接在正負(fù)12 V的電源上。

評(píng)論