基于TLV1562的四通道高速實時數據采集系統的設計

下列條件:

VREFP=AVDD-1V ;

AGND+0.9VVREFM ;

3V>=(VREFP-VREFM)>=0.8V 。

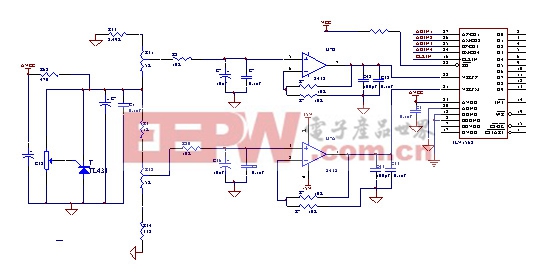

所以設計中采用圖3所示的基準設計。通過調整R31和R32,使VREFP與VREFM滿足上訴要求。

2.3 采集系統的設計

2.3.1 接口時序圖

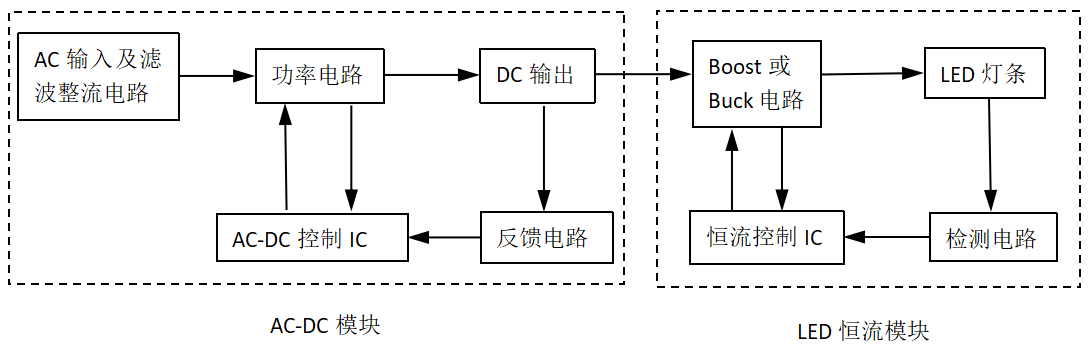

CPLD與TLV1562的接口時序圖見圖3。DISTANCE_PULSE是距離門脈沖,周期為512μs(80Km)或1024μs(160Km),SAMPLE_PULSE是采樣開始脈沖,一旦監測到其上升沿采集系統就開始啟動,START被置為高電平,TLV1562的CS置為低。WR、RD、INT的時序圖是TLV1562的內部轉換模式時序圖。當WR出現兩次低電平后,便完成了對寄存器CR0和CR1的配置,即實現了A/D轉換的初始化。A/D轉換結束,輸出低電平信號INT有效,信號RD讀取A/D轉換結果并復位INT信號,完成一個轉換周期,并開始準備下一次轉換。

|

| 圖3 EP1K100與TLV1562的接口時序圖 |

評論