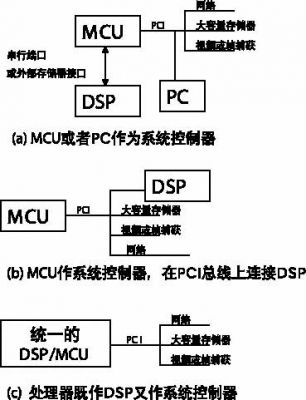

淺論PCI 9 O 5 2芯片功能及其應用

1.3 PCI9052的應用操作

1.3.1 初始化

在上電時,PCI總線的RST#信號將PCI9052的內部寄存器設置為缺省值,同時,PCI9052輸出局部復位信號(LRESET#),并且檢查EEPROM是否存在。如果設備上裝有EEPROM,且EEPROM的第一個16字節非空,那么,PCI9052根據EEPROM或PCI主機CPU設置內部寄存器,否則設為缺省值。

1.3.2 復位

PCI9052總線接口在RST信號輸入有效時將引起整個PCI9052的復位,并輸出LRESET局部復位信號。PCI總線上的主機可以通過設置控制寄存器中的軟件復位比特來對PCI9052進行復位,并輸出LRESET信號。

1.3.3 訪問串行EEPROM接口

復位后,PCI9052開始讀串行EEPROM,若讀出的第一個字非FFFFH,則PCI9052繼續讀操作,否則認為EEPROM無效。對PCI9052來講,EEP-ROM的前四個字節應為52H、90H、B5H和10H,其中9052H為設備號,10B5H為廠商編號。

1.3.4 訪問內部寄存器

PCI9052提供了二種類型的片內寄存器,即PCI配置寄存器和局部配置寄存器,二者都只能由PCI總線和串行EEPROM訪問,也可以通過設置寄存器CNTRL[3:12]禁止對后者的訪問,這樣就極大地增強了接口設計的靈活性。

1.3.5 直接數據傳輸模式

PCI9052支持PCI總線上的主處理器對局部總線上的設備進行讀/寫操作。PCI9052配置寄存器能夠訪問映射到局部的地址空間。同時片內的讀寫FIFO使PCI9052能夠支持PCI總線與局部總線間的高性能猝發傳送。PCI總線主控訪問局部總線的示意圖如圖2所示。

1.3.6 PCI中斷(INTA#)的產生

要產生P C I中斷IN TA#, 首先將寄存器INTCSR[6](PCI中斷使能位)設置為“1”,如果需要以軟件方式產生中斷,則只需將INTCSR[7](軟件中斷位)設置為“1”。如果系統設計方案中選用由局部總線上的設備產生中斷信號INTi1和INTi2,再生成PCI中斷INTA#的方式,只要將寄存器INTCSR的相關位按表1進行設置,復位后INTCSR的值全部為“0”。

評論