3種二進制序列信號檢測器的實現方案

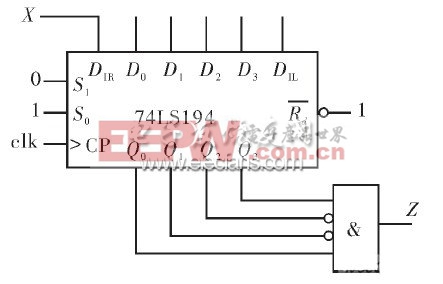

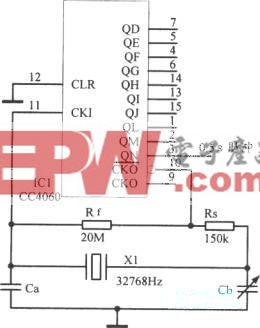

既然用移位寄存器可以實現序列信號檢測,那么用集成移位寄存器加少量門電路同樣可以實現,而且電路可靠性更高。用4位集成移位寄存器74LS194,實現的序列1001檢測器,如圖6所示。

圖6 用集成移位寄存器構成序列碼檢測器

4 當序列不可重疊時的電路設計

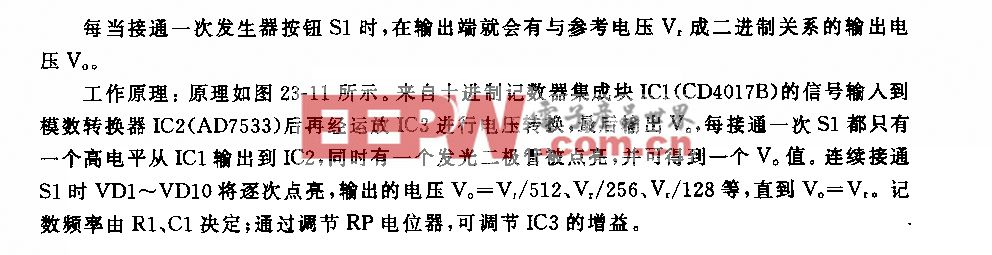

用以上3種方法設計出的電路,都是可序列重疊的序列碼檢測器,若要求被檢測的序列不可重疊,則在方法1中,只需要根據實際情況修改狀態轉換表即可。后面的設計原理及步驟不變。這種設計方法存在的問題仍然是當待檢測的序列位數較長時,設計工作量大、電路可靠性降低。在采用第2、第3種方法設計時,需增加部分控制電路,為保證輸入與時鐘的同步性,需要使得每當檢測出一個序列時,直接將序列的下一位置入寄存器最低位,同時置寄存器其余各位為序列碼最后一位的反碼以消除重疊代碼的影響。此外再用一個鎖存器使輸出高電平多保持0.5個時鐘周期,其優點是:可以消除移位過程中的競爭冒險,使得輸出波形更穩定、電路可靠性更高,電路如圖7所示。

圖7 用移位寄存器構成的序列不可重疊的序列碼檢測器

評論