多個AD9779TxDAC器件的同步

簡介

AD9779 TxDAC的DAC輸出采樣速率最高可達1 GSPS.在某些應用中,例如需要波束導引的應用,用戶可以同步多個AD9779.因此,當AD9779以接近最高速度工作時,TxDAC時序特性變得至關重要。

本應用筆記不討論AD9779運作涉及到的全部細節。若要全面了解其內部數字引擎,用戶應參閱AD9779數據手冊。本應用筆記擴展了SYNC_I的使用,使多個AD9779器件實現相同的REFCLK/DATACLK同步。

在傳統的插值TxDAC中,當DAC采用DAC輸出采樣速率時鐘驅動時,會產生兩個問題。第一,可能難以確定輸入數據在哪一個DACCLK沿鎖存。多數DAC解決這一問題的方法是提供一個DATACLK信號輸出,以指示輸入寄存器鎖存沿的位置。第二個問題發生于用戶試圖同步多個TxDAC時,這是本應用筆記的主題。多個器件的DATACLK輸出并不保證同步,上電時僅靠器件本身不大可能實現同步。AD9779解決這一問題的方法是為數據同步提供第二個時鐘,該時鐘稱為SYNC_I,是AD9779的一路輸入,可以用來同步多個AD9779的輸入數據鎖存。

本應用筆記將詳細說明用于同步多個AD9779器件的數字數據輸入的方法。DAC輸出的相位對齊通過設計保證,精度小于一個DACCLK輸出周期。然而,由于輸出延遲不匹配(室溫下及冷熱溫度下),多個DAC輸出的相位對齊可能存在細微的不一致,本應用筆記不討論這一問題。

同步方案

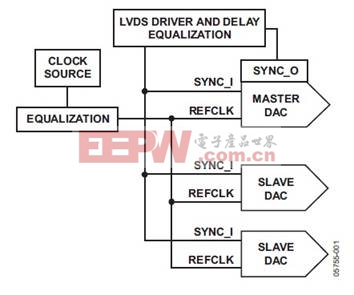

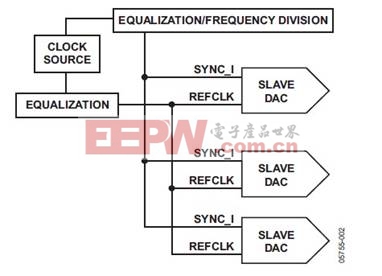

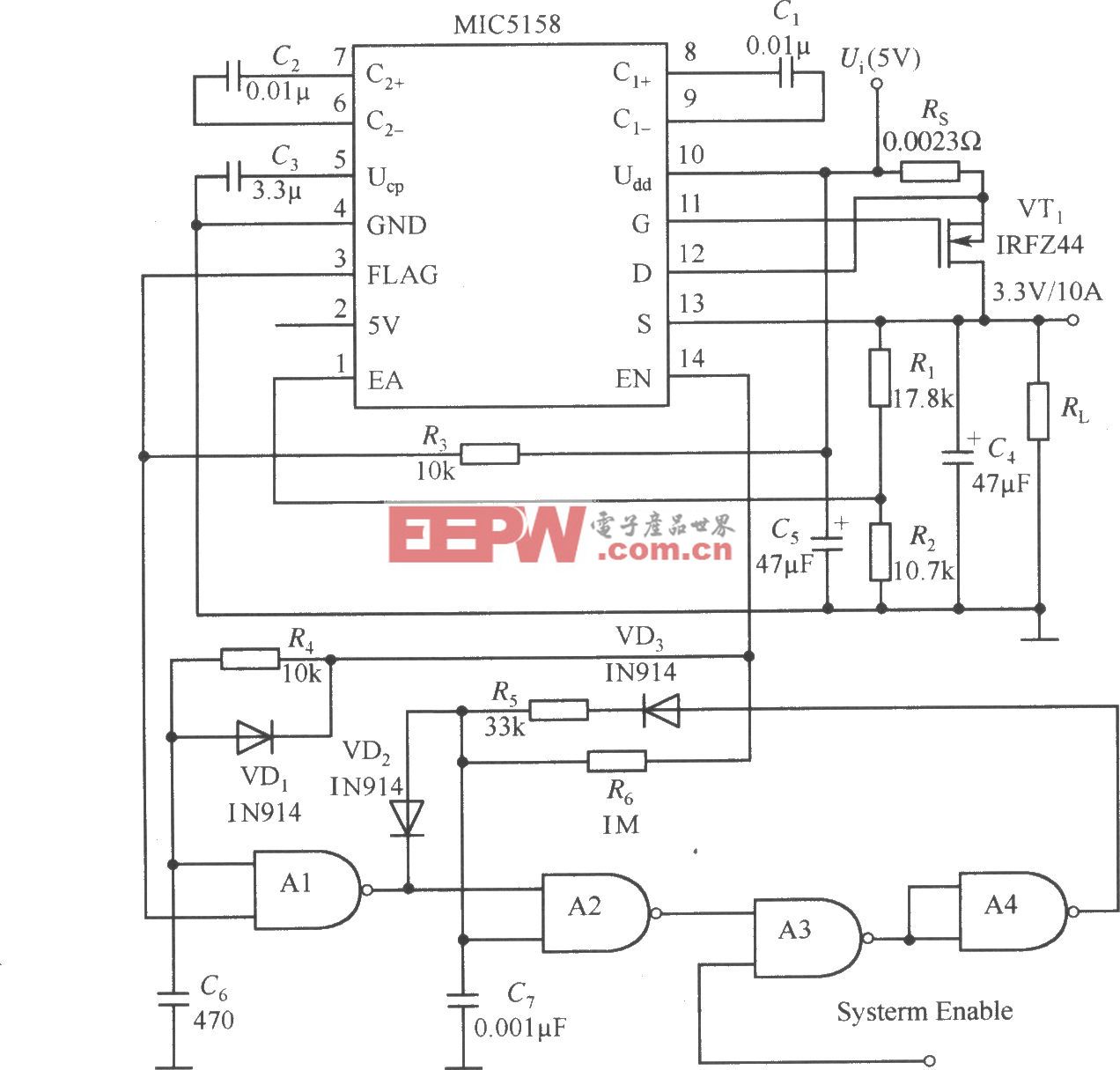

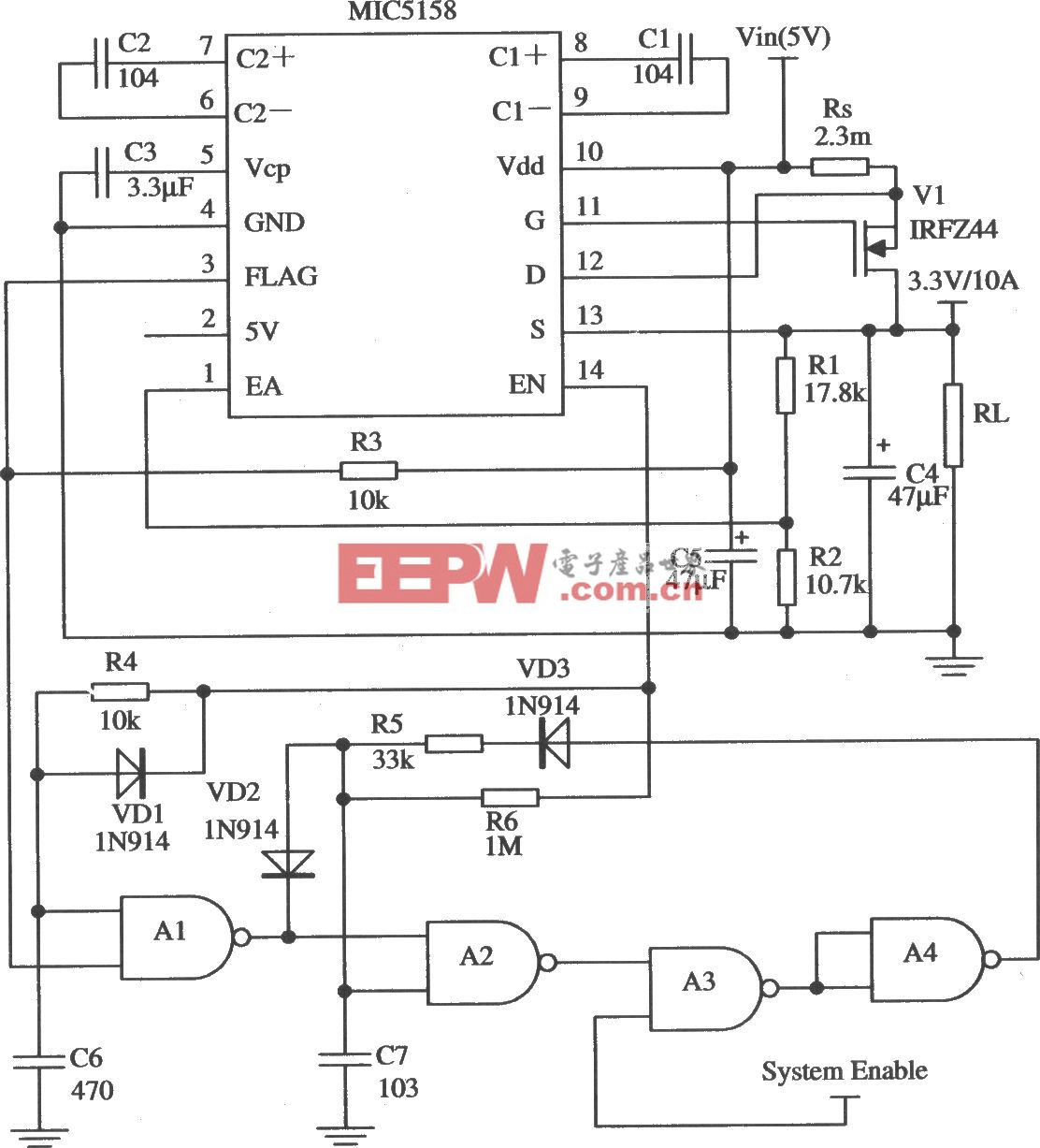

同步多個AD9779 DAC有兩種方案。在第一種方案中,一個器件用作主器件,其余器件用作從器件。在第二種方案中,所有器件都是從器件。兩種方案具有相同的時序限制,不存在性能權衡。主/從模式和從模式的框圖分別如圖1和圖2所示。

圖1. 主/從SYNC_I/O分配

圖2. 從SYNC_I分配

同步詳解

工作中,差分時鐘信號驅動所有主器件和從器件的AD9779 REFCLK輸入。REFCLK輸入接收器是一個高增益差分放大器,各差分輸入需要接近400 mV的共模輸入電平和至少400 mV p-p的擺幅。

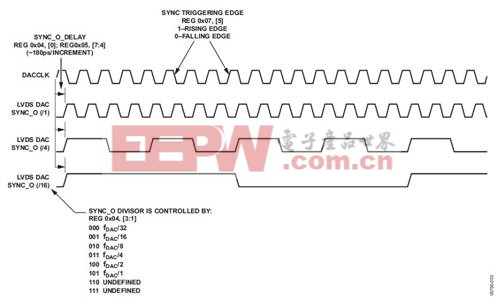

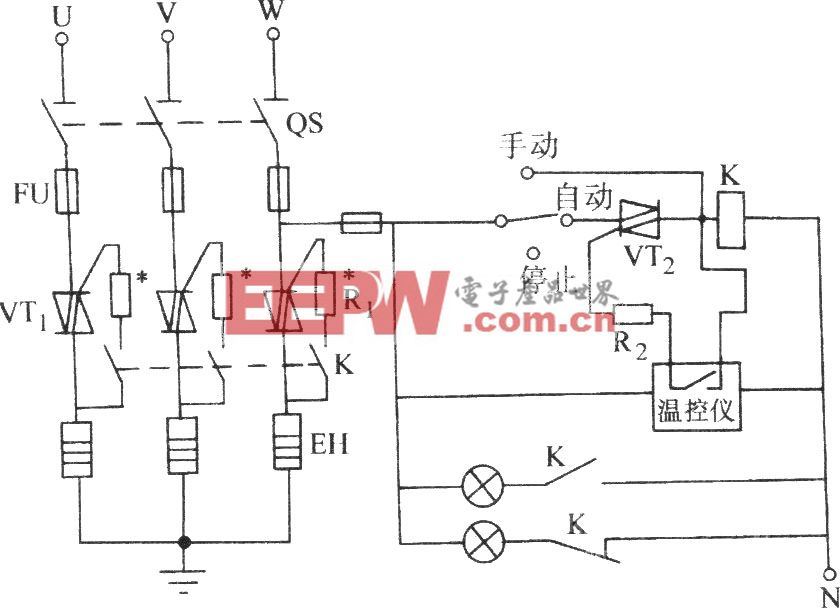

如果選定了主器件,可以使能主器件的差分LVDS輸出信號,該信號稱為SYNC_O+和SYNC_O?.通過寄存器0x07的位5,可以將SYNC_O設置為在DACCLK的上升沿或下降沿觸發。SYNC_O還有一個可編程的延遲,可以通過寄存器0x04的位0 (MSB)和寄存器0x05的位[7:4] (LSB)設置。SYNC_O通過將同步驅動器使能位(寄存器0x07的位6)置1而使能。SYNC_O信號速度可以是REFCLK速度的整數除數,通過寄存器0x04的位[3:1]設置。主器件的REFCLK輸入和SYNC_O信號的可能時序情況如圖3所示。

圖3. DACCLK SYNC_O時序

SYNC_O驅動器和SYNC_I接收器規定用于LVDS電平(參見AD9779數據手冊)。

驅動多個AD9779器件的CMOS數字數據輸入的并行數字輸入總線在時間上應均衡。如果多條數據總線不均衡,可以利用AD9779的編程能力,通過DATA_CLOCK_DELAY(寄存器0x04的位[7:4])以大約180 ps的增量偏移各AD9779的鎖存時間。AD9779無法補償單條數據總線中包含的位偏斜。

在所有AD9779器件上,SYNC_I、REFCLK輸入與CMOS數字輸入數據之間都存在建立保持關系。AD9779數據手冊的時序信息部分說明了這些時序關系。

SYNC_O和SYNC_O_DELAY的推薦應用是利用SYNC_O_DELAY來均衡SYNC_I和REFCLK的時序,確保其時序關系有效。

SYNC_I具有其自己的可編程延遲,可以通過寄存器0x05的位0 (MSB)和寄存器0x06的位[7:4] (LSB)設置。SYNC_I_DELAY可以用于均衡不理想或者選用圖2所示電路的應用中。SYNC_I通過將同步接收器使能位(寄存器0x07的位7)置1而使能。

表1顯示了增量延遲SYNC_O_DELAY和SYNC_I_DELAY,這些延遲可以通過SPI寄存器設置。

表 1

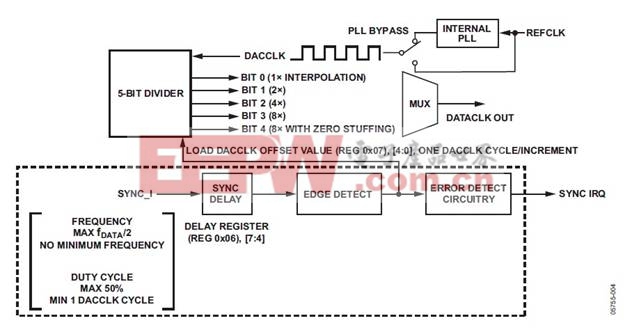

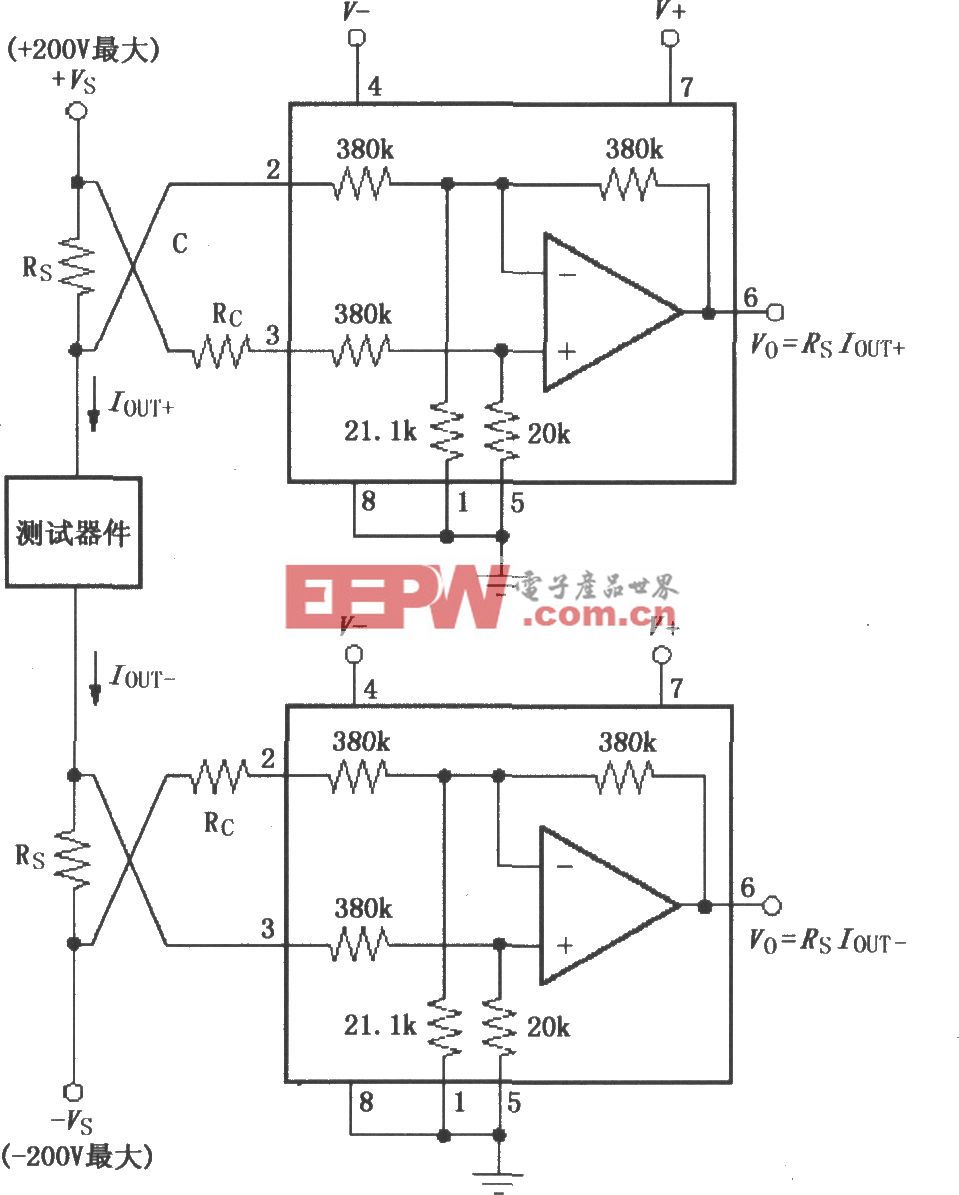

圖4所示為用于同步多個AD9779的內部電路框圖。在可編程的延遲后,SYNC_I信號得到處理,使得對于SYNC_I的每個上升沿,只剩下一個長度為DACCLK周期的脈沖。注意在這種情況下,DACCLK代表AD9779 DAC的內部采樣速率時鐘,它可以與REFCLK相同,具體取決于對AD9779的編程。長度為DACCLK周期的該單一脈沖驅動圖4中的5位分頻器的負載信號。分頻器延遲邏輯的5信號輸出代表所有插值速率的可能DATACLK信號,包括使能零填充的可能性。通過設置DACCLK偏移寄存器,圖4中的位1至位4可以DACCLK周期為增量進行延遲。5位分頻器的內部時序、負載信號的影響和DACCLK偏移值如圖6所示。

圖4. AD9779多DAC同步電路框圖

邊沿檢測器還驅動誤差檢測電路,圖5更詳細地顯示了該電路。可編程誤差檢測電路可以用來測量時序裕量,如果超出時序裕量,將產生中斷。

評論