高速PCB串擾分析及其最小化

3.2串擾引起的時序延時本文引用地址:http://www.czjhyjcfj.com/article/181026.htm

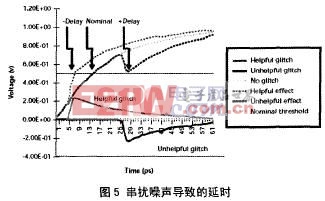

在數(shù)字設(shè)計中,時序問題是一個重要考慮的問題。圖5顯示了由串擾噪聲引起的時序問題。圖下半部分是干擾源網(wǎng)絡(luò)產(chǎn)生的兩種噪聲脈沖(Helpful圖5串擾噪聲導(dǎo)致的延時glitch和Unhelpful glitch),當噪聲脈沖(helpful glitch)疊加到被干擾網(wǎng)絡(luò),就引起被干擾網(wǎng)絡(luò)信號傳輸延時減少;同樣,當噪聲脈沖(Unhelpful glitch)疊加到被干擾網(wǎng)絡(luò)時,就增加了被干擾網(wǎng)絡(luò)正常傳輸信號的延時。盡管這種減少網(wǎng)絡(luò)傳輸延時的串擾噪聲對改善PCB時序是有幫助的,但在實際PCB設(shè)計中,由于干擾源網(wǎng)絡(luò)的不確定性,這種延時是無法控制的,因而對這種串擾引起的延時必須要加以抑制。

4.串擾最小化

串擾在高速高密度的PCB設(shè)計中普遍存在,串擾對系統(tǒng)的影響一般都是負面的。為減少串擾,最基本的就是讓干擾源網(wǎng)絡(luò)與被干擾網(wǎng)絡(luò)之間的耦合越小越好。在高密度復(fù)雜PCB設(shè)計中完全避免串擾是不可能的,但在系統(tǒng)設(shè)計中設(shè)計者應(yīng)該在考慮不影響系統(tǒng)其它性能的情況下,選擇適當?shù)姆椒▉砹η蟠當_的最小化。結(jié)合上面的分析,解決串擾問題主要從以下幾個方面考慮:

在布線條件允許的條件下,盡可能拉大傳輸線間的距離;或者盡可能地減少相鄰傳輸線間的平行長度(累積平行長度),最好是在不同層間走線。

相鄰兩層的信號層(無平面層隔離)走線方向應(yīng)該垂直,盡量避免平行走線以減少層間的串擾。

在確保信號時序的情況下,盡可能選擇轉(zhuǎn)換速度低的器件,使電場與磁場的變化速率變慢,從而降低串擾。

在設(shè)計層疊時,在滿足特征阻抗的條件下,應(yīng)使布線層與參考平面(電源或地平面)間的介質(zhì)層盡可能薄,因而加大了傳輸線與參考平面間的耦合度,減少相鄰傳輸線的耦合。

由于表層只有一個參考平面,表層布線的電場耦合比中間層的要強,因而對串擾較敏感的信號線盡量布在內(nèi)層。

通過端接,使傳輸線的遠端和近端終端阻抗與傳輸線匹配,可大大減小串擾的幅度。

5.結(jié)束語

數(shù)字系統(tǒng)設(shè)計已經(jīng)進入了一個新的階段。許多過去處于次要地位的高速設(shè)計問題,現(xiàn)在已經(jīng)對于系統(tǒng)性能具有關(guān)鍵的影響。包括串擾在內(nèi)的信號完整性問題帶來了設(shè)計觀念、設(shè)計流程及設(shè)計方法的變革。面對新的挑戰(zhàn),對于串擾噪聲而言,最關(guān)鍵的就是找出那些對系統(tǒng)正常運行真正有影響的網(wǎng)絡(luò),而不是盲目的對所有網(wǎng)絡(luò)進行串擾噪聲的抑制,這也是和有限的布線資源相矛盾的。本文所討論的串擾問題對于高速高密度電路設(shè)計中解決串擾問題具有十分重要的意義。

評論