基于FPGA和DDS的數控信號源的設計與實現

2 電路設計與實現

系統中循環相位累加器、ROM表和地址信號發生器是關鍵部分,它們直接決定系統性能。

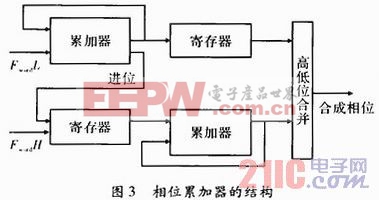

2.1 相位累加器結構設計

為得到足夠高的分辨率,文中循環相位累加器字長取32位。但是,若直接采用32位串行加法器作為累加器,則引入的延遲較大,從而大大降低系統的工作速度。為此,文中采用超前進位原理和流水線技術設計32位循環累加器,其原理框圖如圖3所示。每4位超前進位加法器作為一個基本單元,4個4位超前進位加法器組成16超前進位加法器,并且將入流水技術加入16位超前進位加法器中。最后再將兩個16位加法器組成32位加法器,如圖3所示。本文引用地址:http://www.czjhyjcfj.com/article/177446.htm

2.2 ROM查找表設計

理論上,一個周期內樣點數越多,輸出的波形精度越高。但樣點數越多,需要的存儲空間也越多。為了得到一定精度的波形,又不希望大幅度地增加存儲容量,人們提出如下方法:(1)利用CORDIC及其改進算法來設計DDS。(2)根據抽樣定理,存儲最少的樣點數,每個周期采用固定的樣點數。(3)利用波形的對稱性來減少ROM,如正弦波只需存儲前1/4周期的波形數據。

ROM查找表設計的標目是減少ROM的容量,同時不能過多增加系統的復雜度。根據采樣定理,每個波形周期只需采樣45°,135°,225°,315°相位點對應的4個樣值,就可以無失真地重構模擬波形信號。為保證波形質量,文中每個周期固定采樣32個點,則3種波形有96個樣點,每個樣點用8為二進制數表示,則共需要768 bit。因此,地址信號發生器可設計為32進制的計數器。

ROM查找表結構如圖4所示,其中頭N個樣值為正弦波數據,最后N個樣值為三角波數據,中間是方波數據。若要輸出正弦波,則從第1個存儲單元開始查找;要輸出方波,則從第N+1個單元開始查找,依次類推,圖中N取32。

傳統DDS技術中隨著波形頻率的增加,采樣點數明顯減少,使得波形質量也大大降低。采用這種方法,不管輸出波形多大,采樣點數都是固定的,從而避免以上問題。

評論