寬帶大動態AGC電路設計

利用一個23 dB的耦合器/衰減器,可以讓所需的VGA最大輸出功率與AD8318線性工作范圍的上限(900 MHz時約為-5 dBm)相匹配。

檢波器的誤差放大器利用以地為參考的電容引腳CFLT對誤差信號(電流形式)進行積分。必須將一個電容與CFLT相連,用來設置環路帶寬,并確保環路穩定性。本文引用地址:http://www.czjhyjcfj.com/article/176880.htm

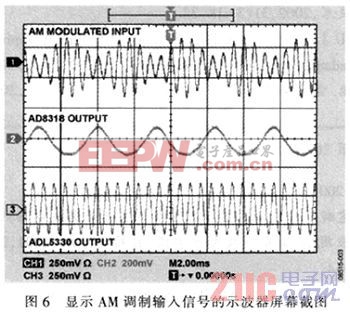

AGC環路能夠控制接近ADL5330完整60 dB增益控制范圍的信號。在通常極為重要的最高功率范圍內,其溫度性能最精確。在輸出功率的最高40 dB范圍內,整個溫度范圍的線性一致性誤差在±0.5 dB范圍內。對數放大器所帶來的寬帶噪聲可忽略不計。為使AGC環路保持均衡,AD8318必須跟蹤ADL5330輸出信號的包絡,并向ADL5330的增益控制輸入提供必要的電平。圖6所示為圖5中AGC環路的示波器屏幕截圖。將采用50%AM調制的100 MHz正弦波施加于ADL5330。ADL5330的輸出信號為恒定的包絡正弦波,其振幅與AD8318的設定點電壓1.5 V相對應。圖中還顯示了AD8318對不斷變化的輸入包絡的增益控制響應。

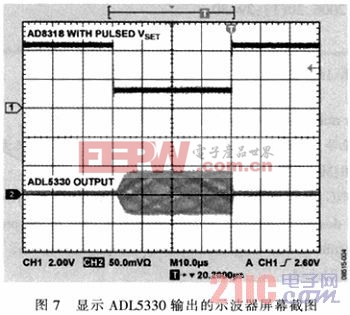

圖7顯示AGC RF輸出對VSET脈沖的響應。當VSET降至1 V時,AGC環路以RF突發脈沖予以響應。響應時間和信號積分量由AD8318 CFLT引腳上的電容控制,這與積分放大器周圍的反饋電容類似。電容增加將導致響應速度變慢。

4 結束語

文中采用新型VGA芯片和對數放大器設計并開發了寬帶大動態AGC電路模塊。在電路設計過程中,采用了一系列優化設計技術,克服了設計過程中的一系列技術難點。經測試,該電路能很好地滿足AGC電路的工作帶寬、動態范圍、線性度等性能參數要求。

評論