基于CS8422的24位多格式立體聲數字音頻接收技術

24-bit, 192-kHz, Asynchronous Sample Rate Converter with Integrated Digital Audio Interface Receive

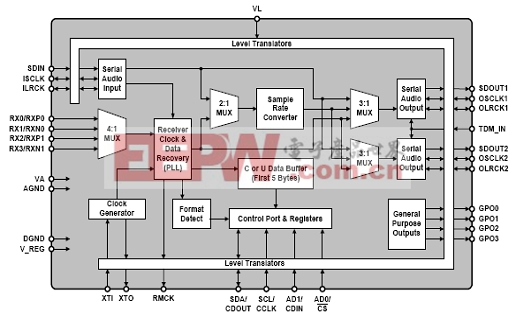

r The CS8422 is a 24-bit, high-performance, monolithic CMOS stereo asynchronous sample rate converter with an integrated digital audio interface receiver that decodes audio data according to the EIAJ CP1201, IEC-60958, AES3, and S/PDIF interface standards.

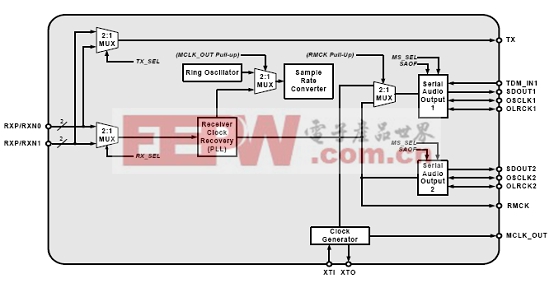

Audio data is input through the digital interface receiver or a 3-wire serial audio input port. Audio is output through one of two 3-wire serial audio output ports. Serial audio data outputs can be set to 24, 20, 18, or 16-bit word-lengths. Data into the digital interface receiver and serial audio input port can be up to 24-bits long. Input and output data can be completely asynchronous, synchronous to an external clock through XTI, or synchronous to the recovered master clock.

The CS8422 can be controlled through the control port in Software Mode or in a Stand-Alone Hardware Mode. In Software Mode, the user can control the device through an SPI or I²C control port.

Target applications include digital recording systems (DVD-R/RW, CD-R/RW, PVR, DAT, MD, and VTR), digital mixing consoles, high-quality D/A, effects processors, computer audio systems, and automotive audio systems.

The CS8422 is available in a space-saving QFN package in both Commercial (-40℃ to +85℃) and Automotive (-40℃ to +105℃) grades. The CDB4822 is also available for device evaluation and implementation suggestions.

CS8422主要特性:

Sample Rate Converter Features

140 dB Dynamic Range

-120 dB THD+N

No External Master Clock Required

Supports Sample Rates up to 211 kHz

Input/Output Sample Rate Ratios from 6:1 to 1:6

Master Mode Master Clock/Sample Rate Ratio Support: 64, 96, 128, 192, 256, 384, 512, 768, 1024

16, 18, 20, or 24-bit Data I/O

Dither Automatically Applied and Scaled to Output Resolution

Multiple Device Outputs are Phase Matched

Digital Audio Interface Receiver Features

Complete EIAJ CP1201, IEC-60958, AES3, S/PDIF Compatible Receiver

28 kHz to 216 kHz Sample Rate Range

2:1 Differential AES3 or 4:1 S/PDIF Input Mux

De-emphasis Filtering for 32 kHz, 44.1 kHz, and 48 kHz

Recovered Master Clock Output: 64 x Fs, 96 x Fs, 128 x Fs, 192 x Fs, 256 x Fs,384 x Fs, 512 x Fs, 768 x Fs, 1024 x Fs

49.152 MHz Maximum Recovered Master Clock Frequency

Ultralow-jitter Clock Recovery

High Input Jitter Tolerance

No External PLL Filter Components Required

Selectable and Automatic Clock Switching

AES3 Direct Output and AES3 TX Passthrough

On-chip Channel Status Data Buffering

Automatic Detection of Compressed Audio Streams

Decodes CD Q Sub-Code

System Features

SPI or I²C Software Mode and Stand-Alone Hardware Mode

Flexible 3-wire Digital Serial Audio Input Port

Dual Serial Audio Output Ports with Independently Selectable Data Paths

Master or Slave Mode Operation for all Serial Audio Ports

Time Division Multiplexing (TDM) Mode

Integrated Oscillator for use with External Crystal

Four General-purpose Output Pins (GPO)

+3.3 V Analog Supply (VA)

+1.8 V to 5.0 V Digital Interface (VL)

Space-saving 32-pin QFN Package

圖1. CS8422方框圖

圖2.CS8422軟件模式連接框圖

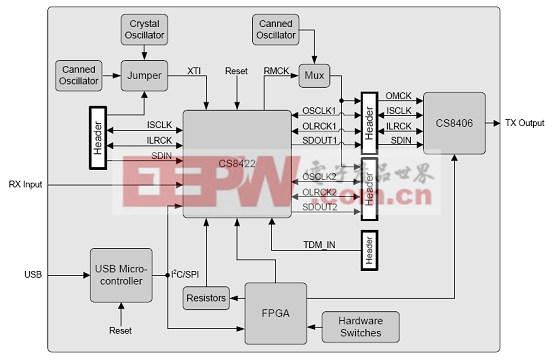

圖3.CS8422硬件模式連接框圖

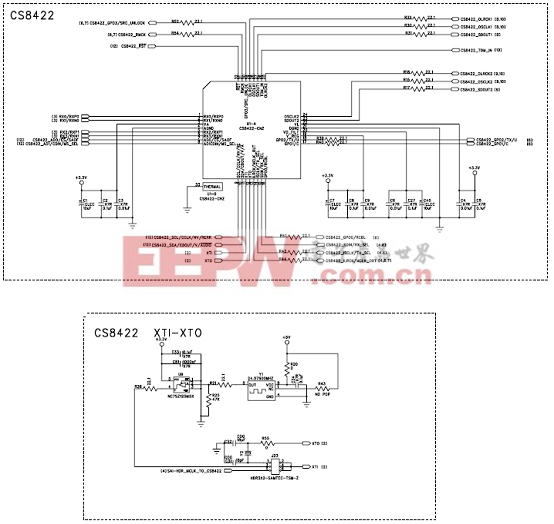

圖4.CS8422硬件模式時鐘路徑圖

CS8422評估板CDB8422

Using the CDB8422 evaluation board is an ideal way to evaluate the CS8422. Use of the board requires a digital signal source, an analyzer, and a power supply. A Windows PC-compatible computer is also required if using software mode to configure the CDB8422.

S/PDIF and AES3/EBU input connections are made via RCA phono, optical, or XLR connectors to the CS8422. S/PDIF output connections are made via RCA phono or optical connectors from the CS8406 (S/PDIF Tx). System timing can be provided by a S/PDIF or AES3/EBU input signal, by the CS8422 with supplied master clock, or by an I/O stake header with a DSP connected.

The provided Windows-based software GUI makes configuring the CDB8422 easy. The software communicates through the PC’s USB port to configure the board so that all features of the CS8422 can be evaluated.

The board may also be configured without a PC connection by using hardware switches; however, not all configurations of the CDB8422 are possible in hardware mode.

CS8422評估板CDB8422主要特性:

IEC-60958, AES3/EBU, S/PDIF Inputs

C Single-Ended Inputs via Optical and RCA Input Jacks

C Differential Inputs via XLR Input Jack

S/PDIF Outputs

C Optical and RCA Output Jacks

C CS8406 Digital Audio Transmitter

I/O Stake Headers

C External Control Port Accessibility

C External Serial Audio I/O Accessibility

3.3 V Logic Interface

Powered by Single External Power Supply or PC USB Port Connection

H/W Control via DIP Switches

FlexGUI S/W Control - Windows® Compatible

C Pre-Defined User-Configurable Scripts

圖5.評估板CDB8422方框圖

評論