用于天文觀測(cè)的CCD相機(jī)系統(tǒng)的研究

關(guān)鍵詞:CCD CPLD 相關(guān)雙采樣 控制系統(tǒng) 串口通信

引言

CCD通常分為3個(gè)等級(jí);商業(yè)級(jí)、工程級(jí)和科學(xué)級(jí)。3個(gè)級(jí)別的要求一級(jí)比一級(jí)高。衡量CCD的性能主要從以下幾個(gè)方面:量子效率和響應(yīng)度、噪聲等效功率和探測(cè)度,即動(dòng)態(tài)范圍和電荷轉(zhuǎn)移效率等。科學(xué)級(jí)CCD以其高光子轉(zhuǎn)換效率、寬頻譜響應(yīng)、良好線性度和寬動(dòng)態(tài)范圍廣泛用于天文觀測(cè),已成為望遠(yuǎn)鏡測(cè)必不可少的后端設(shè)備。國內(nèi)各天文臺(tái)望遠(yuǎn)鏡終端都是從外圍引起的成套設(shè)備,使用和維護(hù)很不方便,并且價(jià)格昂貴,因此國內(nèi)迫切需要發(fā)展自己的CCD技術(shù)。紫金山天文臺(tái)紅外實(shí)驗(yàn)室對(duì)這一課題進(jìn)行了深入研究,廣泛調(diào)研,認(rèn)真選取,從芯片開始一直到系統(tǒng)的軟硬件設(shè)計(jì),搭建了自己的CDD相機(jī)系統(tǒng)。

1 系統(tǒng)設(shè)計(jì)

CCD芯片決定相機(jī)系統(tǒng)的性能,為此我們廣泛調(diào)研,最后選定柯達(dá)公司的KAF-0401LE芯片。它動(dòng)態(tài)范圍大(70dB),電荷轉(zhuǎn)移效率高(0.999 99),波長響應(yīng)范圍寬(0.4μm~1.0μm),低暗電流(在25℃條件下,7pA/cm2),量子效率為35%,并且具有抗飽和性,能夠滿足科學(xué)觀測(cè)的要求,既可用于光譜分析,又可用于成像觀測(cè)。

系統(tǒng)設(shè)計(jì)的重點(diǎn)是解決CCD芯片的驅(qū)動(dòng)和系統(tǒng)噪聲的問題。我們的設(shè)計(jì)如下:采用柯達(dá)公司的KAF-0401LE芯片作為探測(cè)器,Ateml公司的帶閃存Flash的89C51作下位機(jī)控制器,復(fù)雜可編程邏輯作(CPLD)作時(shí)序發(fā)生和地址譯碼,采用相關(guān)雙采樣技術(shù)降低噪聲,自帶采樣保持的12位A/D轉(zhuǎn)換順AD1674進(jìn)行模數(shù)轉(zhuǎn)換,擴(kuò)展8片128Kbit(628128)的RAM作1為幀圖像暫存空間,通過RS232與計(jì)算機(jī)串口通信,接受計(jì)算機(jī)的控制。整個(gè)系統(tǒng)由圖1所示幾個(gè)功能部件組成。

1.1 時(shí)序信號(hào)發(fā)生電路

KAF-0401LE芯片的時(shí)序要求:積分期間φV1、φV2保持低電平;行轉(zhuǎn)移期間φH1保持高電平,φH2保持低電平。每行開始φV1的第2個(gè)脈沖下降沿后,要有1個(gè)行轉(zhuǎn)移建立時(shí)間tφHs,讀完行后需延遲1個(gè)像素時(shí)間te才開始下一行φV1脈沖;同樣,φV1第2分脈沖下降沿后,開始下一行轉(zhuǎn)移,如此直到讀完1幀。

復(fù)雜可編程邏輯器件(CPLD)以其高度集成、靈活、方便的特點(diǎn),在電路設(shè)計(jì)中運(yùn)用越來越廣泛。Altera公司的復(fù)雜可編程邏輯器件EPM712SLC84-15具有2500個(gè)可用邏輯門,128個(gè)宏單元,8個(gè)邏輯塊,最大時(shí)鐘可達(dá)147.1MHz,帶有68個(gè)可供用戶使用的I/O引腳,PLCC封裝,可通過JTAG接口實(shí)現(xiàn)在線編程。我們選用EMP7128SLC84-15,通過硬件描述語言(VHDL)在集成開發(fā)環(huán)境MAX PLUS II下完成邏輯設(shè)計(jì);編譯后,通過JTAG接口下載到電路板上的EPM7128SLC84-15中,實(shí)現(xiàn)了KAF-0401LE芯片的時(shí)序要求。

MAX PLUS II雖然有很豐富的元件庫,但并不是針對(duì)某一應(yīng)用而開發(fā)的,具有通用性,調(diào)用它固有的元件庫可能造成資源的浪費(fèi),沒有必要。因此我們按照需求,編制了自己的元件庫,然后在程序中作為元件調(diào)用。在本系統(tǒng)中,僅用1片EPM7128LC84-15就實(shí)現(xiàn)了CCD的時(shí)序要求、暫存RAM和接口擴(kuò)展芯片8255的片選和地址譯碼,既簡(jiǎn)化恥電路的硬件設(shè)計(jì),提高了系統(tǒng)可靠性,又降低了成本。交流時(shí)序條件要求如表1所列。

表1

| 描 述 | 符號(hào) | 最小值 | 正常值 | 最大值 |

| φH1、φH2時(shí)鐘頻率/MHz | fH | 10 | 15 | |

| φV1、φV2時(shí)鐘頻率/kHz | fV | 100 | 125 | |

| 周期/ns | te | 67 | 100 | |

| φH1、φH2建立時(shí)間/μs | tφHS | 0.5 | 1 | |

| φV1、φV2脈沖/μs | tφv | 4 | 5 | |

| 復(fù)位時(shí)鐘脈寬/ns | tφR | 10 | 20 | |

| 讀出時(shí)間/ms | treadout | 34 | 50 | |

| 每行讀出時(shí)間/μs | tline | 65.8 | 95.6 |

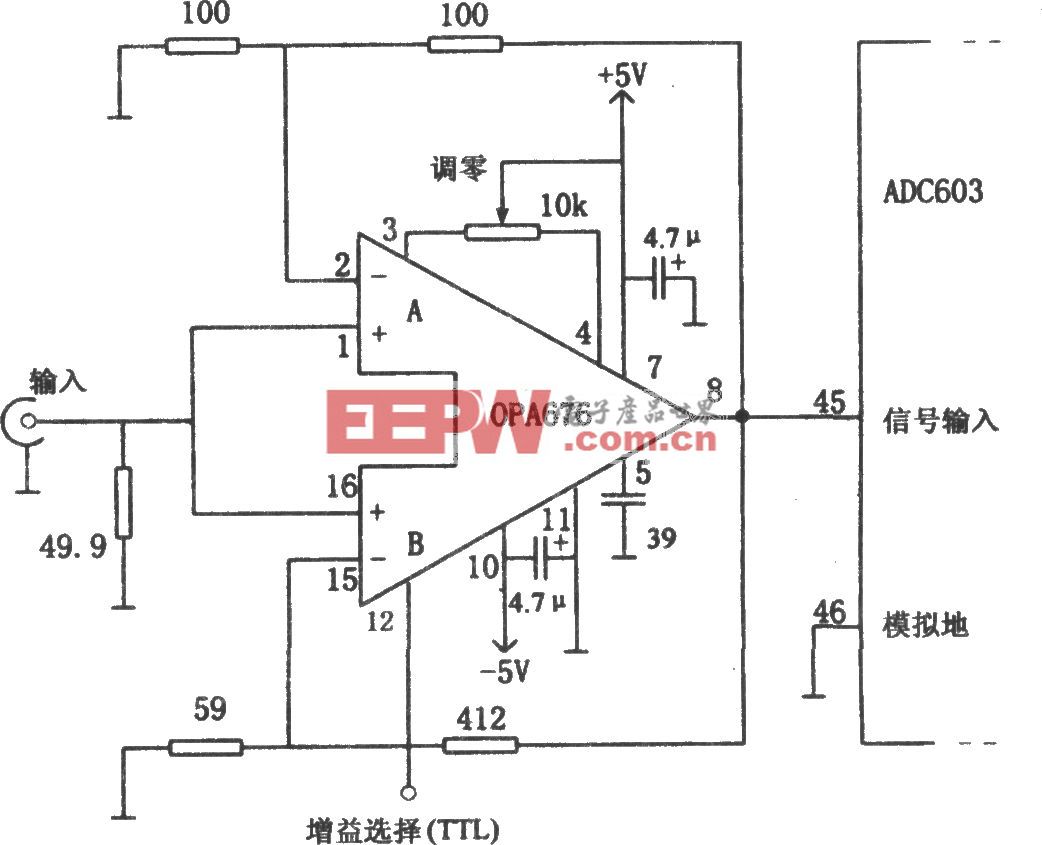

1.2 雙采取、模擬放大電路及A/D變換電路

我們采用能夠滿足高頻要求的放大器LF356N設(shè)計(jì)雙采樣和模擬放大電路。根據(jù)CCD的動(dòng)態(tài)范圍選用自帶采樣保持的12位A/D變換器AD1674作模數(shù)轉(zhuǎn)換。

雙采樣原理如圖2所示。RSL是CCD復(fù)位電平,光信號(hào)相當(dāng)于SGL與RSL的差值,理論上只要分別在RSL和SGL處各采樣一次,然后相減便得到信號(hào)的值。然而,實(shí)際上RSL和SGL并不是理想的水平線,而是存在著低頻起伏噪聲。為了降低噪聲的影響,通常的做法是,分別在RSL和SGL處多次采樣求平均,這樣對(duì)硬件和數(shù)據(jù)處理軟件的要求都很高。我們這里采用了積分型相關(guān)雙采樣技術(shù),如圖3所示,CCD信號(hào)分別經(jīng)過同相和反相放大器連到模擬開關(guān)輸入端。模擬開關(guān)S1打開時(shí),RSL通過電容積分;s2打開時(shí),SGL信號(hào)經(jīng)電容積分;s3打開輸入端接地,信號(hào)保持不變;s4為復(fù)位開關(guān)。積分放大器的輸入、輸出關(guān)系如下:

圖2中的積分輸出是相關(guān)雙采樣的輸出波形圖。采樣保持后通過A/D進(jìn)行模數(shù)轉(zhuǎn)換,經(jīng)8255口存在板上的RAM中。

1.3 電壓偏置電路

CCD驅(qū)動(dòng)信號(hào)的直流偏置電壓各不相同,CPLD產(chǎn)生的TTL信號(hào)必須經(jīng)過電壓變換才能加到CCD的輸入端。我們首先用LM317和LM337產(chǎn)生所需要的偏置電壓,然后經(jīng)過時(shí)鐘驅(qū)動(dòng)芯片DS0026轉(zhuǎn)換得到時(shí)序和偏置都符合CCD要求的信號(hào),電路如圖4所示。

其中,Iadj100μA,Vref=1.25V,圖4(a)中R1取240Ω,圖4(b)中R1取120Ω。

2 軟件編程

軟件是管理硬件的工具,硬件是實(shí)現(xiàn)軟件功能的基礎(chǔ)。本系統(tǒng)的軟件工作任務(wù)較重,從可編程邏輯器件的硬件描述語言編程、電路板上單片機(jī)的匯編程語言編程,到計(jì)算機(jī)上控制系統(tǒng)的Visual C++編程。

2.1 時(shí)序信號(hào)的VHDL語言編程

我們用VHDL編制CCD時(shí)鐘驅(qū)動(dòng)信號(hào)、圖像暫存RAM和接口擴(kuò)展芯片8255的地址譯碼和片選信號(hào),在集成開發(fā)環(huán)境MAXPLUS II中編譯,通過JTAG口下載到EPM7128SLC84-15中。下面給出實(shí)現(xiàn)CCD系統(tǒng)時(shí)序部分VHDL語言設(shè)計(jì)和時(shí)序仿真結(jié)果。VHDL語言編程基本上分為2個(gè)部分:實(shí)體說明和結(jié)構(gòu)體定義。實(shí)體說明部分定義端口,結(jié)構(gòu)體中實(shí)現(xiàn)邏輯設(shè)計(jì)。程序如下:

LIBRARY ieee; --包括的庫

USE ieee.std_logic_1164.all;

USE ieee.std_LOGIC_ARITH.ALL;

USE ieee.std_logic_unsigned.all;

ENTITY kodak7128 IS --實(shí)體說明部分

PORT --端口

( clk:IN std_logic; 時(shí)鐘輸入

start:IN STD_LOGIC; --啟動(dòng)采集數(shù)據(jù)輸入

rc:OUT STD_LOGIC; --啟動(dòng)A/D變換輸出

s1,s2,s3,s4:OUT STD_LOGIC; --相關(guān)雙采樣模式時(shí)鐘輸出

v1:OUT STD_LOGIC; --CCD行轉(zhuǎn)移時(shí)鐘輸出

v2:OUT STD_LOGIC;

r :OUT STD_LOGIC;--CCD復(fù)位始終輸出

h1:OUT STD_LOGIC;--CCD像素轉(zhuǎn)換時(shí)鐘信號(hào)輸出

h2: OUT STD_LOGIC;

a,b,c:IN STD_LOGIC; --擴(kuò)展RAM譯碼輸入

a2,a3,a4,a5,a6,a7:IN STD_LOGIC; --口擴(kuò)展芯片8255地址譯碼片選輸入

a8,a9,a10,a11,a12,a13,a14,a15 : IN STD_LOGIC;

ram5,ram6,ram7:OUT STD_LOGIC; --擴(kuò)展RAM及8255片選譯碼輸出

ram8,ram9,ram10,ram11,ram12,cs8255:out std_logic);

ARCHITECTURE mboard OF kodak7128try IS-結(jié)構(gòu)體實(shí)現(xiàn)部分

--PROCESS定義邏輯

END mboard;

時(shí)序仿真結(jié)果如圖5所示。

2.2 下位機(jī)的匯編語言編程

89C51作為電路板上的靈魂,負(fù)責(zé)接收計(jì)算機(jī)傳來的命令,管理CCD數(shù)據(jù)的采集、接收、傳送。與計(jì)算機(jī)的通信通過串行口中斷實(shí)現(xiàn),數(shù)據(jù)的采集通過外中斷實(shí)現(xiàn)。

事先需要定義好計(jì)算機(jī)與單 牒同的通信協(xié)議,在初始化程序中設(shè)置通信波特率、堆棧初始化以及寄存器初值,然后進(jìn)入循環(huán),等待中斷的發(fā)生,調(diào)用中斷子程序,實(shí)現(xiàn)預(yù)定功能。

2.3 CCD相機(jī)控制系統(tǒng)Visual C++編程

Windows以其操作簡(jiǎn)單、友好的圖形界面成為最流行的操作系統(tǒng)。Visual C++是目前公認(rèn)最強(qiáng)大的Windows程序設(shè)計(jì)工具。我們用它開發(fā)了相機(jī)控制系統(tǒng)。

首先定義人機(jī)接口的操作界面。在程序中主要分為數(shù)據(jù)的獲取、存儲(chǔ)與處理幾個(gè)方面,在數(shù)據(jù)的獲取方面我們專門定義一個(gè)串口通信類,開一個(gè)線程用于監(jiān)聽串口事件的發(fā)生,用于向下位單片機(jī)發(fā)送命令和接收數(shù)據(jù)。

3 測(cè)試結(jié)果

我們完成了從芯片到相機(jī)系統(tǒng)的軟硬件研制,初步測(cè)試,效果良好,對(duì)于發(fā)展我們自己的CCD技術(shù)做出有意義的探索和研究。圖6是相機(jī)CCD量子效率測(cè)試結(jié)果。

評(píng)論