如何實現微控制器與FPGA的接口設計

因為處理器專門負責維持PIO工作,所以處理時間消耗很大。雖然CPU是從事數據傳輸,它還是不能做別的事了。因此,這一解決方案有可能使系統處理陷入癱瘓。DMA不可能使用的PIO接口,所以程序員必須限制的數據帶寬,以便其他任務能夠與MCU進行通訊。例如,如果有一個常規的進程要求100 %的處理器運行周期,同時又要與FPGA進行串行(SPI,USART或TWI)通信(讀或寫),那么這兩個進程必須有一個要等待。如果發送到或接受來自FPGA的數據沒有及時的存進緩沖區,那么到下一個字節/字數據時可能會溢出。從本質上講,嵌入式處理器成為受??賴的數據移動硬盤。

通過外部總線接口連接(EIB)

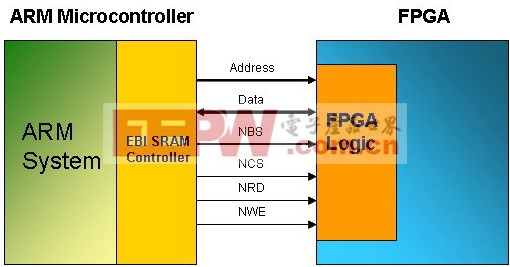

許多32位微控制器有一個外部總線接口(EBI)模塊,它是為外部設備和基于ARM設備的存儲控制器之間傳輸數據而設計的。這些外部存儲控制器能夠處理幾種類型的外部存儲器和外圍設備,如SRAM,PROM,EPROM,EEPROM,flash和SDRAM。只要FPGA可以處理預定義存儲器接口,EBI也可用于FPGA的接口。在EBI中使用靜態存儲器接口(SRAM)對于FPGA通信來說是最好的,因為它設計簡單,且大多數設計者都熟悉它。至于PIO接口, FPGA不得不包含一個模塊,用來理解SRAM時間,并能產生一個響應返回微控制器(圖4)。

圖4 EBI-SMC接口

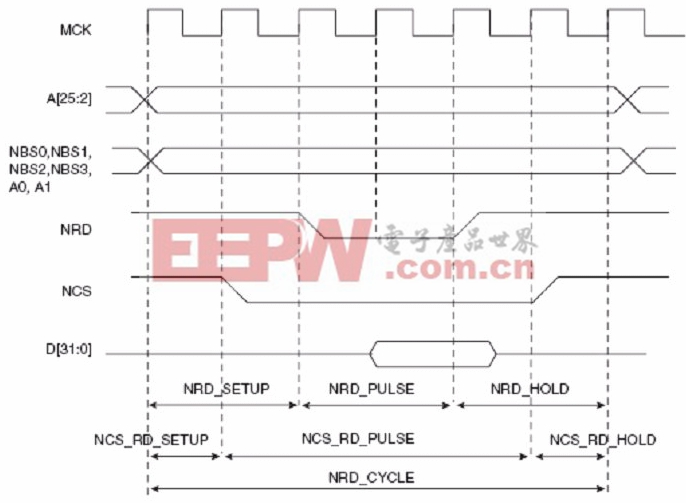

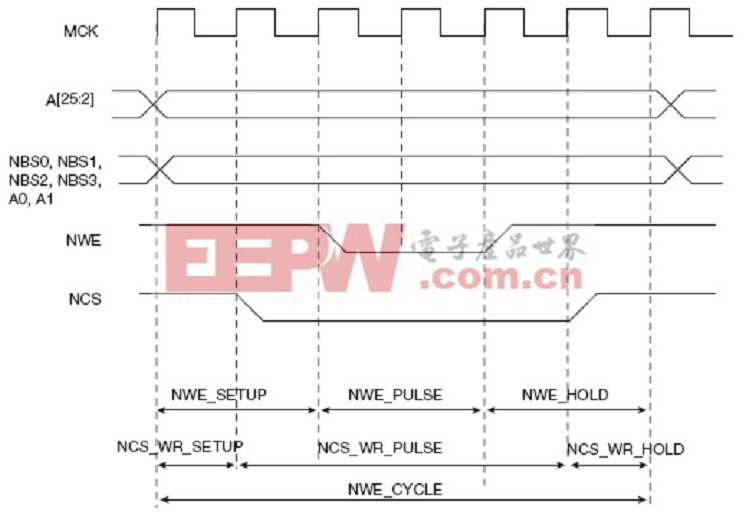

圖5顯示了EBI讀SMC存儲器接口的標準時間,而圖6顯示了其標準寫周期。

圖5 EBI-SMC讀周期

圖6 EBI-SMC寫周期

注意:這些時間波形是默認的SMC規格。所有可編程參數顯示都基于外部設備的速度。

EBI的接口速度比PIO塊,是因為EBI有其自己的I / O,且大部分的信號是并行的。但是,如果外部設備很慢或引入等待狀態, EBI的速度優勢可能會受到損害。

跟PIO接口一樣, EBI接口必須由處理器或其他的主AHB來驅動。因此,實現帶寬的EBI的還依賴于軟件,并取決于它可以利用多少處理器時間。當然,可能受到帶寬的限制。這又可能限制了嵌入式處理器旨在實現的其他系統功能。

評論