音頻信號數字化光纖傳輸實驗儀信道的設計與實現

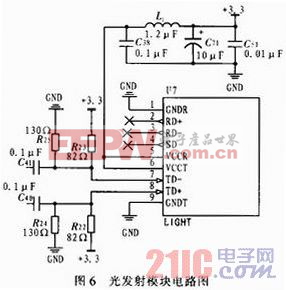

2.4.2 電/光模塊

采用型號為HNMS-XEMC41XSC20,工作波長在T1310 nm/R1550 nm的單纖雙向一體化收發模塊,將電信號差分數據流轉成光數據信號流,電路如圖6所示。本文引用地址:http://www.czjhyjcfj.com/article/154036.htm

2.5 信號的接收及處理

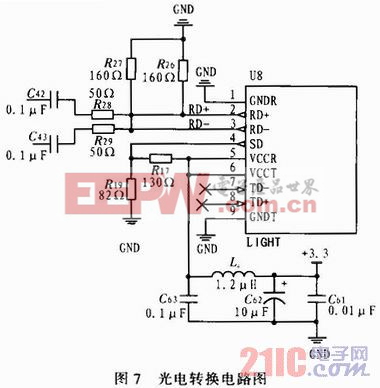

2.5.1 光/電轉換模塊

該實驗裝置以單纖進行信號傳輸,光信號傳輸到接收裝置后,需要還原為電信號,即差分電壓數據流。采用型號為HNMS-XEMC41XSC20,工作波長在T1310nm/R1550nm的單纖雙向一體化收發模塊,將光信號轉換為電信號。轉換后的差分信號由RD+和RD-輸出,電路如圖7所示。

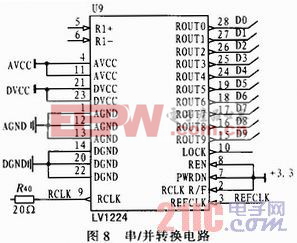

2.5.2 串并轉換

串并轉化裝置采用與發送器中的串化器SN65LV1023A相匹配的解串器SN65LV1224A。發送器中的串化器將10位的并行數據轉換為串行的差分數據流,因此在接收器中需用相應的解串器將串行差分數據流還原為并行數據。

SN65LV1224A內部有鎖相環,在接收數據流時可以根據數據的頻率自行匹配接收時鐘,外界只需為其提供參考時鐘。此處參考時鐘選為18.432 MHz,由FPGA控制部分提供。芯片還匹配了與解串后的數據同步的時鐘,以助于轉換后的并行數據輸出。為了保證音頻信號的連續性和實時性,需避免芯片處于省電模式或高阻模式。因此PWRDN和REN需接高電平。RCLK-R/F接高電平,即選擇時鐘上升沿輸出數據電路如圖8所示。

該組芯片有兩種同步方式:快速同步和隨機同步。快速同步是由串化器發送一組由連續的6個“1”和“0”組成的同步信號,解串器收到信號后鎖定數據時鐘,鎖定完成之前LOCK保持高電平,同步完成后跳變為低電平。同步信號的發送是由串化器的SYNC1和SYNC2控制的,只要兩者之一置高電平持續時間超過6個時鐘周期,串化器就開始連續發送同步信號。快速同步具有快速準確的優點,但在長距離的信號傳輸中,光纖只傳遞數據,無法很好的傳遞串化器和解串器的SYNC和LOCK信號。因此采用隨機同步方式。

隨機同步方式串化器不需發送同步信號,解串器直接對數據流進行鎖定,實現同步,鎖定丟失后,解串器會重新鎖定時鐘。將LOCK接到FPGA以進行實時控制。

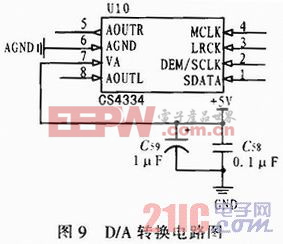

2.6 D/A轉換及視頻信號輸出

D/A轉化部分采用Cirrus Logic公司出品的專業音頻信號處理芯片CS4334。其具有完善的立體聲DAC系統,抗干擾能力強,失真噪聲小,采用單電壓+5 V電源,電路如圖9所示。

芯片具有兩種時鐘模式,即外部串行時鐘模式和內部串行時鐘模式。當芯片工作在外部串行時鐘模式下時,去加重濾波器不能被訪問,且外部串行時鐘易被干擾,故本裝置設計時采用了內部串行時鐘模式。串行時鐘SCLK在內部產生,并與主時鐘MCLK(18.432 MHz)、采樣時鐘RLCK(96 KHz,由FPGA分頻產生)同步。信號經數模轉化后,分別由AOUTL和AOUTR輸出左右聲道模擬信號,經低通濾波后輸出,由于滿量程時信號最大輸出可達3.5 V,且裝置可通過外接放大器進行聲音信號的放大,故在本設計中未進行音頻信號的放大處理。

數字通信相關文章:數字通信原理

評論