基于散列DMA的高速串口驅動設計

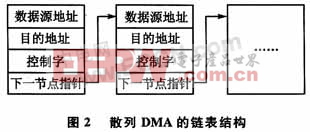

DMA數據傳輸可分為塊傳輸和散列傳輸兩種方式。在DMA傳輸數據的過程中,要求源物理地址和目標物理地址必須是連續的。但是在某些計算機體系中(如IA架構),連續的存儲器地址在物理上不一定是連續的,所以DMA傳輸要分成多次完成。傳輸完一塊物理上連續的數據后引發一次中斷,然后進行下一塊物理上連續的數據傳輸,這就是DMA塊傳輸方式(Block DMA)。散列傳輸是在塊傳輸方式上發展起來的,它與一個傳輸鏈表相關,如圖2所示。該鏈表可以是單向結構或環形結構。控制字中包含數據位寬、數據塊大小、當前塊傳輸結束是否引發中斷等控制信息。DMA塊傳輸可看作是只含有一個節點,且下一節點指針總是指向當前節點的散列傳輸。采用散列DMA方式能更靈活、高效地傳輸數據。

3.1 硬件平臺

SPEAR300是ST公司在ARM926EJ-S核的基礎上開發的高性能嵌入式處理器。其最高工作頻率為333MHz,有8個獨立的DMA通道,支持散列DMA;UART支持DMA傳輸,發送和接收FIFO大小均為16字節,在192 MHz的外設總線(APB)頻率下支持的最高波特率為12 Mbps,如果提高APB的頻率還可以獲得更高的波特率。本文的硬件平臺是以SPEAR300為核心的人機界面產品,主要外設包括觸摸屏、液晶顯示模組、網口和串口(串口要支持最高波特率為12 Mbps的西門子MPI通信協議)。

串口驅動程序的核心是實現數據高效穩定的收發。為了實現UART的高速數據傳輸,UART中斷設置為最高優先級;同時在操作系統中允許中斷嵌套,打開UART接收超時中斷RTI并使能UART的DMA傳輸。這樣,當UART的發送FIFO數據減少到設定的參考值(FIFOLevel)時,發送DMA傳輸就會被觸發。同樣,當接收FIFO的數據增長到設定值時,接收DMA傳輸就會被觸發。為了減少DMA傳輸被觸發的次數同時保證數據被及時傳輸,發送FIFO Level設定為2字節,而接收FIFOLevel設定為14字節,將發送和接收的FIFO Level分別設定為0和16字節是有很大風險的。MPI協議要求傳輸的一幀數據不能有間斷,所以在使用DMA傳輸UART數據時DMAC必須獨占系統總線。為了避免產生緩存一致性問題,使用2塊非緩存內存區域存放待發送的數據和已接收到的數據。

發送數據時,待發送的數據量總是已知的。先構造一個傳輸節點,數據源地址為數據包的首地址,目的地址為UART寄存器,數據位寬為8,下一節點指針(PTR_NEXT)為空。當前數據包發送結束前,如果PTR_NEXT被更新,則下一個數據包的傳輸自動開始。當前數據包是否發送完畢,可通過讀取DMAC寄存器DMACCnControl的TransferSize字段得知。整個發送數據的過程無需觸發任何中斷,流程圖如圖3所示。如果采用DMA塊傳輸方式,就需要在每次傳輸完畢后產生DMA中斷,重新裝載數據到內存中的發送數據區以發送下一個數據包。

評論