Cyclone II如何實現的DDR SDRAM接口

Cyclone II器件支持如SDR SDRAM,DDR SDRAM,DDR2 SDRAM以及QDRII RAM等外部存儲器接口。下面將著重討論Cyclone II器件如何實現DDR SDRAM接口控制的。

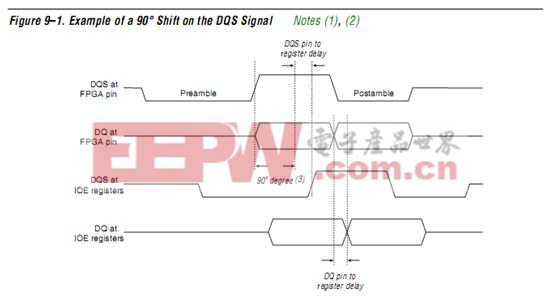

Cyclone II器件有專用的與DDR SDRAM接口的data(DQ),data strobe(DQS),clock管腳。一般是8個DQ信號對應與1個DQS信號,DQS信號和DQ信號從DDR SDRAM輸出時是沿對齊的。進入FPGA后要想實現中心對齊,即DQS的變化沿與DQ的中心對齊,那么必須在FPGA內部對DQS做延時處理,如Figure 9-1所示。

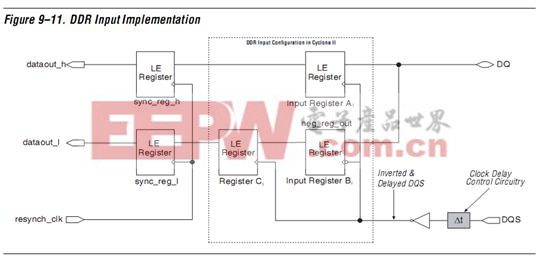

DDR輸入接口實現如Figure 9-11所示。這也是一個涉及到異步時鐘域數據通信的問題,且看它是如何進行同步的。resynch_clk是FPGA內部使用的時鐘,DQS相對與和DQ同步的時鐘。這兩個時鐘其實是同頻不同相,相位偏移肯定是要滿足FPGA的采樣時鐘和數據信號中心對齊,這涉及到DDR SDRAM的輸出時鐘信號的相位調整。

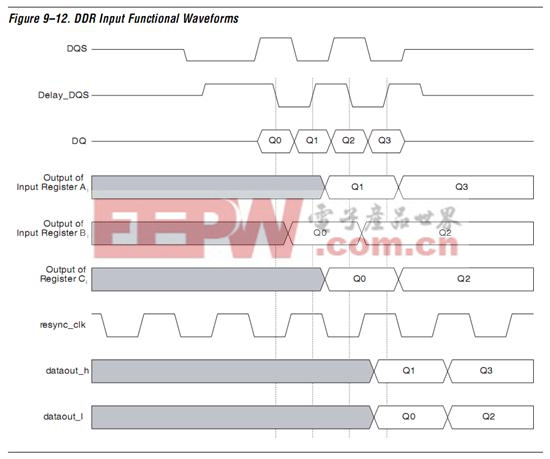

輸入信號DQS經過反向延時后與DQ信號中心對齊,然后分別使用方向延時后的DQS信號的下降沿和上升沿鎖存DQ信號前后輸入的數據Q0和Q1,同時在上升沿時會對前一級采樣的Q0信號再進行一次鎖存,從而使Q0和Q1信號在被FPGA同步時鐘采樣前達到同頻同相。FPGA內部時鐘通過對經過處理后的Q0和Q1信號采樣達到了雙沿數據輸入的采樣。詳細波形如Figure 9-12所示。

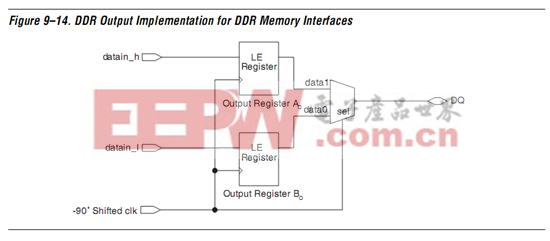

DDR輸出接口實現如Figure 9-14所示。經過90度相移的DDR SDRAM時鐘先對FPGA內部時鐘域的待輸出信號進行一次鎖存,然后由相移時鐘的高低電平選擇作為當前輸出給DDR SDRAM的數據信號。

詳細波形如Figure 9-15所示。

評論