Altera器件時間匹配問題的解決方案

2.3 重新設計電路

毛刺是信號趨于穩定前不必要的開關動作,使每個時鐘沿改變了寄存器間組合邏輯的輸入。對每個節點而言,不同的輸入路徑有不同的延時,這將多次改變狀態。節點上的毛刺多少與該節點的邏輯深度,也就是節點至最初輸入的邏輯門個數有關。到達節點的邏輯錐體越深、越寬,毛刺也越多。降低邏輯深度,減少邏輯錐體的開關輸入可減少這類毛剌。時序驅動合成以及邏輯單元的合理映射能減少邏輯級的數量。

如果一個計數器的輸出端接一個組合電路,這個組合電路的輸出端產生了毛刺,最好的解決方法是重新設計電路,只要在這一時刻改變計數器輸出端子的輸出順序,就可以消除下一級組合電路輸出端的毛刺。例如,在下面程序中,在這一時刻改變q0、q1、q2輸出順序,就能解決計數器輸出所接的組合電路輸出端毛刺的問題。

subdesign modcount

(clk,reset:input;

q[2..0]

utput;

utput; )

variable

counter3:machine of bits(rr[2..0])

with states(r0=B101, --換成r5的輸出

r1=B100, --換成r4的輸出

r2=B000, --換成r0的輸出

r3=B001, --換成r1的輸出

r4=B011, --換成r3的輸出

r5=B010, --換成r2的輸出

r6=B110,

r7=B111);

begin

q[ ]=rr[ ];

counter3.reset=reset;

counter3.clk=clk;

CASE counter3 IS

when r0=>counter3=r1;

when r1=>counter3=r2;

when r2=>counter3=r3;

when r3=>counter3=r4;

when r4=>counter3=r5;

when r5=>counter3=r6;

when r6=>counter3=r7;

when r7=>counter3=r0;

END CASE;

End ;

3 行波時鐘時間匹配問題

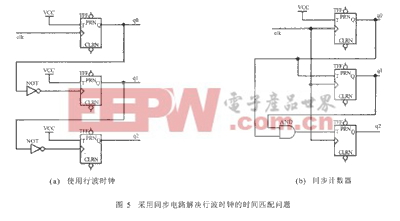

行波時鐘是計數器通常使用的一種時鐘方式,而使用行波時鐘是可能引起潛在時間匹配問題的另一個因素。所謂行波時鐘是指一個寄存器的輸出為另一個寄存器產生時鐘,而不是使用一個公共的系統時鐘。如果仔細設計,行波時鐘可以像全局時鐘一樣可靠工作,但是行波時鐘使得與電路有關的定時計算變得很復雜。行波時鐘在行波鏈上各寄存器時鐘之間將產生較大的時間偏移,并且會超出最壞情況下的建立時間、保持時間和電路中時鐘到輸出的延時,使系統的實際速度下降。在圖5(a)中使用行波時鐘所示電路的時鐘周期依賴于計數器最低位的變化沿計數器傳播到最高位所花的時間,這個周期與計數器的位數有關。隨著逐位進位計數器的位數增加,系統的速度將下降,為此可使用同步電路來解決這個問題,如圖5(b)所示。當把異步計數器改成同步操作時,系統的速度由寄存器的建立和保持時間決定,而不是由計數器的位數決定。同步電路不需要使用附加的資源,就可以提高計數器的速度,并消除出現非法計數數值的可能性。

|

還可以通過在MAX+PLUSII中仔細地分配資源,來提高設計的可靠性。在MAX器件中通過PIA的信號將會有時間延時。為消除這種延時,可以在MAX+PLUSⅡ中進行團體分配,也就是將計數器鄰接的位安排在同一個LAB中的諸宏單元內。

4 結束語

在組合電路中,從信號輸入到穩定輸出需要一定的時間。由于從輸入到輸出的過程中,不同通路上門的級數不同,或者門電路平均延遲時間的差異,使信號從輸入經不同通道傳輸到輸出級的時間不同,由于這個原因,就產生了毛刺。這是一個普遍性的問題。本文對解決毛刺的方法作了一個總結,有利于大家快速、準確設計穩定的集成電路。在這個問題上,AHDL語言比VHDL語言要直觀、易于理解。從宏觀上看,要解決Altera器件設計中的時間匹配問題,要使用同步設計。采用同步電路設計也可以使電路免受外部因素影響(如硅處理工藝和溫度變動)而造成的時間匹配問題。

評論