基于Spantan FPGA的多路數(shù)字量采集模塊設(shè)計(jì)

FPGA內(nèi)部邏輯主要分為數(shù)字信號(hào)采集、數(shù)據(jù)緩存和數(shù)據(jù)讀取、FIFO控制。根據(jù)要求,信號(hào)采集又分為頻率信號(hào)采集、20路數(shù)字信號(hào)采集和15路脈沖信號(hào)采集。系統(tǒng)同時(shí)采集三組信號(hào),再送入外部FIFO中緩存。由于脈沖信號(hào)的數(shù)據(jù)量較大,時(shí)序不匹配,因此在信號(hào)采集完后數(shù)據(jù)還應(yīng)緩存,然后再經(jīng)數(shù)據(jù)編幀送至外部FIFO。內(nèi)部緩存利用VHDL編寫模塊,但是更簡(jiǎn)易的方法是利用FPGA內(nèi)部的雙口RAM。因此,F(xiàn)PGA選用Xilinx公司的XCF2S-100E,其內(nèi)部集成5 KB容量的RAM,足夠內(nèi)部緩存使用。數(shù)據(jù)經(jīng)信號(hào)采集后送人緩存,然后由讀取模塊讀出再送入外部FIFO,整個(gè)模塊采用120 MHz的時(shí)鐘,可以滿足要求大于100 MHz的時(shí)鐘頻率。采集20路數(shù)字信號(hào)的方法是當(dāng)信號(hào)變化時(shí),就將當(dāng)前所有數(shù)字信號(hào)的電平狀態(tài)都送入緩存,而對(duì)于頻率信號(hào)和脈沖信號(hào)的采集則采用如下方法。

4.1 頻率信號(hào)采集

由于頻率信號(hào)只需體現(xiàn)出其頻率大小即可,因此采集頻率信號(hào)時(shí)只記錄該信號(hào)兩沿間的時(shí)間。即就是設(shè)定一個(gè)16位的計(jì)數(shù)器T,計(jì)數(shù)器的值隨主時(shí)鐘累加,當(dāng)判斷到該信號(hào)有變化時(shí),就將計(jì)數(shù)器的值T1送人緩存,然后將該計(jì)數(shù)器清零。計(jì)數(shù)器的值繼續(xù)累加,直到該信號(hào)下一次變化,再將計(jì)數(shù)器的值T2送入緩存,計(jì)數(shù)器再清零,以此類推,來(lái)記錄該信號(hào)兩沿間的時(shí)間。

4.2 脈沖信號(hào)采集

采集脈沖信號(hào)需記錄該信號(hào)的脈寬以及相對(duì)于同步信號(hào)的延遲。記錄方法是:使用一個(gè)單獨(dú)的進(jìn)程,定義一個(gè)24位的計(jì)數(shù)器TB,當(dāng)同步信號(hào)的上升沿到來(lái)時(shí)開(kāi)始計(jì)數(shù),當(dāng)同步信號(hào)的下一個(gè)上升沿到來(lái)時(shí),該計(jì)數(shù)器清零。另一個(gè)進(jìn)程判斷15路脈沖信號(hào)中有一路信號(hào)變化時(shí),將當(dāng)前計(jì)數(shù)器TB的值送人緩存,并將當(dāng)前所有脈沖信號(hào)的電平狀態(tài)都送入緩存。

4.3 數(shù)據(jù)的編幀和解幀

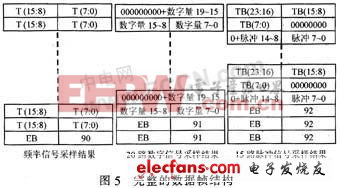

在數(shù)據(jù)采集部分中,當(dāng)同步信號(hào)的上升沿到來(lái)時(shí),將3個(gè)幀標(biāo)志分別寫入3個(gè)緩存,頻率信號(hào)數(shù)據(jù)的幀標(biāo)志為EB90;20路數(shù)字信號(hào)的幀標(biāo)志為2個(gè)EB91;15路脈沖信號(hào)數(shù)據(jù)的幀標(biāo)志為3個(gè)EB92。讀取數(shù)據(jù)模塊中,當(dāng)同步信號(hào)的下降沿到來(lái)時(shí),開(kāi)始讀取緩存的數(shù)據(jù)送至外部FIFO,并判斷當(dāng)讀取一個(gè)EB90后,開(kāi)始讀取緩存的數(shù)據(jù),并送入外部FIFO;當(dāng)讀到兩個(gè)EB91后,讀取緩存的數(shù)據(jù),并送入外部FIFO;當(dāng)讀到3個(gè)EB92后表明一幀數(shù)據(jù)讀取完畢,等待下一個(gè)同步信號(hào)的下降沿后再開(kāi)始讀取下一幀數(shù)據(jù)。由于外部FIFO是16位,所以數(shù)據(jù)中不滿16位的都用0將數(shù)據(jù)補(bǔ)充完整,完整的數(shù)據(jù)幀結(jié)構(gòu)如圖5所示。

上位機(jī)收到一幀數(shù)據(jù)后進(jìn)行解幀處理,對(duì)于頻率信號(hào)數(shù)據(jù),將這些T值相加并求平均得出T’,再乘以2,由于系統(tǒng)時(shí)鐘是120 MHz,所以2T’/120為頻率信號(hào)周期(μs級(jí)),然后求倒數(shù)即可得出該信號(hào)的頻率值。

20路數(shù)字量信號(hào)數(shù)據(jù)直接顯示其電平狀態(tài)。脈沖信號(hào)數(shù)據(jù)則先判斷哪一路(多路)脈沖信號(hào)發(fā)生變化,再判斷該信號(hào)(幾路信號(hào))的電平狀態(tài)。若為高電平,則對(duì)應(yīng)的時(shí)間應(yīng)為TBa;若為低電平,則對(duì)應(yīng)的時(shí)間應(yīng)為TBb。TBa即為該脈沖信號(hào)相對(duì)于同步信號(hào)的延遲,而TBb-TBa的值即為該脈沖信號(hào)的正脈沖脈寬。

5 結(jié)束語(yǔ)

針對(duì)測(cè)控系統(tǒng)監(jiān)測(cè)信號(hào)數(shù)量較多的問(wèn)題,提出了一種基于FPGA的多路數(shù)字量采集與處理模塊,設(shè)計(jì)了相應(yīng)的電路和FPGA邏輯。在綜合調(diào)試成功的基礎(chǔ)上,該多路數(shù)字量采集模塊已成功應(yīng)用于某測(cè)試系統(tǒng)。

隔離器相關(guān)文章:隔離器原理

評(píng)論