基于NIOS II的SOPC存儲(chǔ)器型外設(shè)接口的設(shè)計(jì)

緊耦合數(shù)據(jù)存儲(chǔ)器中的數(shù)據(jù)可以通過(guò)設(shè)定數(shù)據(jù)單元大小后在.hex文件中進(jìn)行初始化。SOPCBuilder編譯成功后,可在Nios II IDE下編寫測(cè)試代碼,以便將初始化文件中的數(shù)據(jù)通過(guò)指向地址的指針讀出。以下是部分測(cè)試代碼:

3 FIFO接口的設(shè)計(jì)

Altera公司已將FIFO內(nèi)嵌到FPGA中,用戶可以根據(jù)不同的設(shè)計(jì)需求來(lái)使用。FIFO的基本單元是寄存器,作為存儲(chǔ)器件,它的存儲(chǔ)能力可由內(nèi)部定義的存儲(chǔ)寄存器的數(shù)量決定,一般以數(shù)據(jù)量的深度X為寬度形式來(lái)說(shuō)明所采用的基本結(jié)構(gòu),它通常是雙端口的存儲(chǔ)器,其中一個(gè)端口用于寫入數(shù)據(jù),另一個(gè)端口用于讀出數(shù)據(jù)。使用時(shí)可以同時(shí)對(duì)存儲(chǔ)器的存儲(chǔ)單元進(jìn)行寫入和讀出操作,而且FIFO型的存儲(chǔ)器不需要由地址來(lái)存取數(shù)據(jù)。它通常需要由另外的信號(hào)線(或標(biāo)志)來(lái)標(biāo)明存儲(chǔ)器的狀態(tài)。

SOPC Builder中沒(méi)有相應(yīng)的FIFO接口控制器,因此需要自己定義FIFO接口。可首先在Quartus II的界面中新建一個(gè).bdf文件,在下拉菜單中選擇MegaWizard Plug-InManager,在打開的選項(xiàng)中從altera提供的庫(kù)中找到FIFO,并根據(jù)需要選擇FIFO的深度及寬度,設(shè)定好參數(shù)后再添加在.bdf中。然后在Ouartus II工程中打開SOPC Builder,并在Create New Comlaonet打開創(chuàng)建元件向?qū)В瑫r(shí)在Signals選項(xiàng)卡中添加端口信號(hào)。由于需要將緊耦合存儲(chǔ)器中的數(shù)據(jù)寫到FIFO中,因此,F(xiàn)IFO的接口信號(hào)有寫使能addr和32位寫數(shù)據(jù)接口writedata等,且時(shí)鐘和處理器的時(shí)鐘信號(hào)相同。FIFO作為外設(shè)存儲(chǔ)器設(shè)備,其地址對(duì)齊方式一般選擇動(dòng)態(tài)地址對(duì)齊。通過(guò)實(shí)驗(yàn)驗(yàn)證FIFO的時(shí)序符合要求后,即可將緊耦合數(shù)據(jù)存儲(chǔ)器中的數(shù)據(jù)寫到FIFO。圖3所示是將緊耦合數(shù)據(jù)存儲(chǔ)器中的數(shù)據(jù)寫人FIFO的時(shí)序驗(yàn)證。

4 SRAM的接口設(shè)計(jì)

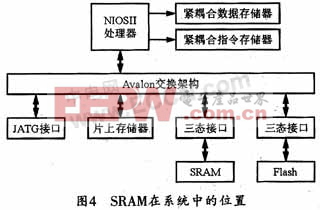

本設(shè)計(jì)中的SRAM采用的是ISSI公司的IS61LV25616AL-10TL型16位高速異步SRAM,它屬于存儲(chǔ)器型外設(shè),因此,地址對(duì)齊方式選擇動(dòng)態(tài)地址對(duì)齊。SRAM可通過(guò)Avalon三態(tài)從端口與Avalon交換架構(gòu)相連接。圖4所示是SRAM在系統(tǒng)中的位置示意圖。

Avalon的三態(tài)特性允許基于Avalon的系統(tǒng)直接與片外設(shè)備相連接,例如存儲(chǔ)器芯片或一個(gè)外部處理器。Avalon三態(tài)從端口允許Avalon SwitchFabric與PCB板上共享的地址和數(shù)據(jù)總線的片外設(shè)備進(jìn)行接口,可用于將Avalon Switch Fabric與同步和異步存儲(chǔ)器芯片的連接。三態(tài)從端口通常使用雙向信號(hào)data,而不是獨(dú)立的、單向信號(hào)readdata和writedata。Data信號(hào)是三態(tài)的,因而允許多個(gè)三態(tài)外設(shè)與數(shù)據(jù)總線相連而不引起信號(hào)沖突。Avalon三態(tài)從端口經(jīng)常使用負(fù)邏輯信號(hào),符合典型的存儲(chǔ)器芯片的約定。Avalon三態(tài)從端口信號(hào)需要注意的是地址信號(hào)。Avalon三態(tài)從端口地址信號(hào)一般代表一個(gè)字節(jié)地址,這與使用字地址的非三態(tài)從端口不同。Avalon三態(tài)從端口的地址信號(hào)可被多個(gè)片外設(shè)備共享,這些設(shè)備可能有不同的數(shù)據(jù)寬度。若Avalon三態(tài)從端口的數(shù)據(jù)寬度比一個(gè)字節(jié)大,則必須將地址信號(hào)從AvalonSwitch Fabric正確映射到從設(shè)備的地址線。

Avalon Switch Fabric信號(hào)直接與具有Avalon三態(tài)從端口的片外異步存儲(chǔ)器相連一般不需要時(shí)鐘信號(hào),而在chipsclest、read或write信號(hào)上的脈沖則使用建立和保持時(shí)間與傳輸同步。

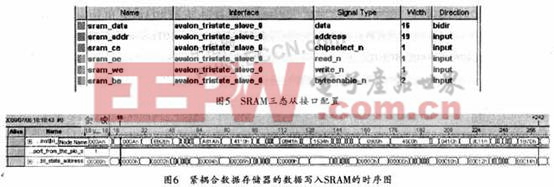

PCB板中有片選、讀寫使能、高低字節(jié)使能、數(shù)據(jù)線、地址線,因此,在SOPC Builder中的Create New Componet中設(shè)置SRAM的信號(hào)線包括數(shù)據(jù)線sram_data、地址線sram_addr、片選sram_ce、讀寫使能sram_oe、we以及字節(jié)使能信號(hào)sram_be。通過(guò)閱讀IS61LV25616AL-10TL型高速異步靜態(tài)RAM手冊(cè)可知,其建立時(shí)間、保持時(shí)間都為40ns,讀等待和寫等待為160ns,這使其既可符合Avalon總線時(shí)序的要求,又符合IS61LN25616AL-10TL型SRAM的時(shí)序要求。圖5所示為SRAM的三態(tài)從接口配置圖,圖6是將緊耦合數(shù)據(jù)存儲(chǔ)器的數(shù)據(jù)寫入SRAM的時(shí)序波形。

5 結(jié)束語(yǔ)

本文通過(guò)將片上和片外存儲(chǔ)器接入SOPC系統(tǒng),介紹了存儲(chǔ)器型外設(shè)接口的定制方法。同時(shí)說(shuō)明了將緊耦合存儲(chǔ)器添加至系統(tǒng),以及將數(shù)據(jù)通過(guò)處理器由存儲(chǔ)器讀寫到存儲(chǔ)器的設(shè)計(jì)方法,并在cyclone EP1C120240C8的FPGA上進(jìn)行了結(jié)果驗(yàn)證,因此,用戶可根據(jù)實(shí)際需要采用此方法將外設(shè)接入Avalon總線,并構(gòu)建SOPC系統(tǒng)。本文引用地址:http://www.czjhyjcfj.com/article/149630.htm

評(píng)論