基于片內WISHBONE總線的高速緩存一致性實現

3總線事務時序分析

由前部分的說明發現在內部總線上可以產生三種類型的總線事務:讀缺失時,塊傳輸總線事務;SM或SC狀態寫命中時,發生單宇寫總線事務;寫缺失時,先是一個塊傳輸總線事務而后在本地寫操作完成后,一個單字寫總線事務更新遠端的數據高速緩存單元。以下是塊傳輸和單字寫總線周期具體的時序分析,下文提到的具體信號其意義可以查閱參考文獻[1]。

塊傳輸時序:主接口通過聲明CYC_O申請總線的使用權,同時也給出STB_O、CTI_0(010)、WE_O(低電平)和ADR_O;經過若干時鐘周期等待后,如果遠端從接口給出ACK_I信號,同時給出的SHARE_I信號為低電平(說明遠端數據高速緩存沒有所需要的數據塊,.SHARE_I為自定義的信號),這時主接口忽略DAT-I信號,下一個時鐘周期撤銷CYC_O信號,結束片內總線周期;如果給出AClI信號的同時,SHARE_I信號為高電平(說明遠端數據高速緩存有所需要的數據塊),接收DAT-I上的數據;而后7個時鐘周期內,每個時鐘周期ADR_O數據加4,DAII上的數據根據地址相應地變化,在第7個數據傳輸的時鐘周期CTI_O變為111,告訴遠端從接口這是最后一個傳輸時鐘周期,下一個時鐘周期:降完成這個總線事務;最后一個時鐘周期主接口撤銷CYC_O信號,結束片內總線周期。

內塊傳輸時序見圖2。

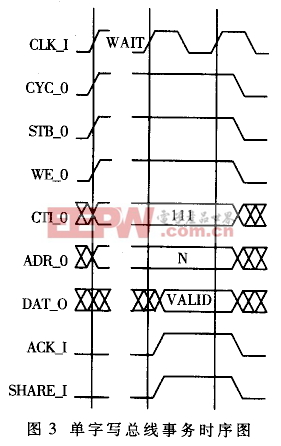

單字寫總線周期:主接口通過聲明CYC_O申請總線的使用權,同時也給出STB_O、CTI_O(111)、WE_O(高電子)、ADlO和DAT-0;經過若干時鐘周期等待后,如果遠端從接口給出ACK_I信號,同時給出的SHARE信號為低電子(說明遠端數據高速緩存沒有所需要的數_I據塊),主接口下一個時鐘周期撤銷CYC_O信號,結束片內總線周期;如果給出ACK_I信號的同時,SHARK-I信號為高電子(說明遠端數據高速緩存有所需要的數據塊),說明從接口已經用DAT-O上的數據更新了相應的數據單元,下一個時鐘周期撤銷CYC_O信號,結束片內總線周期。

單字寫時序見圖3。

塊傳輸總線事務時序圖2,單字寫總線事務時序圖3中WAIT表示主接口等待總線仲裁和從接口的應答,需若干時鐘周期,最快的情況下只要一個時鐘周期。總線仲裁:如果兩個數據高速緩存的主接口同時請求,由仲裁單元決定哪個主接口可以使用片內總線,仲裁的優先級算法是輪換法。數據高速緩存的主接口,在聲明CYC_O申請總線后,如果AClI一直是低電平無效,但同時該數據高速緩存從接口的CYC_I信號有效,說明數據高速緩存主接口沒有得到總線使用權,主接口撤銷CYC_O信號,該數據高速緩存響應從接口的操作,操作完成后,主接口再次聲明CYC_O信號請求總線;相反,如果數據高速緩存主接口的ACK_I信號高電平有效,說明得到了總線使用權,可以使用總線。

綜上所述,片內總線采用WISHBONE總線地址增量的傳輸方式,與內核時鐘同步,最快可以在9個時鐘周期從另一個數據高速緩存調來一個塊(8個宇)的內容,可在2個時鐘周期更新遠端數據高速緩存的一個相關單元;數據高速緩存實現寫回、寫更新機制,減少了向外部總線寫操作的頻度。該結構具有可擴展性,只要把片內WISHBONE·總線的地址線的位數擴展(用于選擇多個從接口)就可以把多個內核集成在該芯片上,協議無需變化。該種體系結構運行兩個耦合度很低的程序,性能最好。

該方案利用WISHBONE總線,基于監聽總線的寫更新一致性協議,把兩個IP核集成在一塊芯片上,實現了單芯片多處理器結構的FPGA。該體系結構采用開放的片上總線標準,具有公用的主從接口規范,實現了IP核可移植性,具有設計可復用的優點。

評論