基于Flash和JTAG的FPGA系統

3.1 設計的FPGA實現

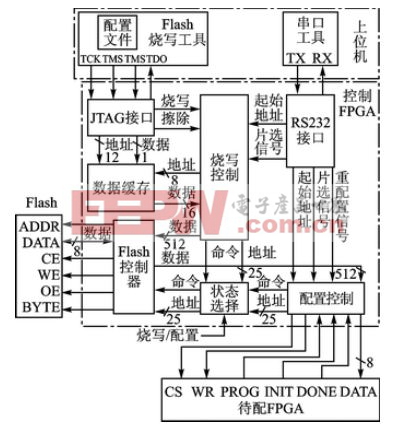

控制FPGA實現的邏輯控制功能包括與上位機軟件iMPACT和串口工具通信、燒寫Flash以及配置FPGA器件。基于模塊化的設計思想將具體功能分解成多個模塊,如圖3所示,數據與地址通道上的下標為其通道寬度。各模塊作用如下:

1,RS232接口模塊接收來自串口工具的配置文件地址及重配置信號,配置文件地址譯碼后得到對Flash存儲器進行各種操作時的起始地址,重配置信號則用來觸發FPGA配置文件的切換。

2,JTAG模塊包括JTAG接口模塊、數據緩存模塊及燒寫控制模塊。JTAG接口接收JTAG下載線上的JTAG指令和數據后,若為FERASE或FPGM指令則向燒寫控制模塊發送擦除或燒寫信號,若為FDATA0指令則接收TDI上的串行數據并存入數據緩存模塊中。數據緩存模塊利用片內BRAM來實現,可存放一幀配置碼流。燒寫控制模塊接收到擦除信號后,產生擦除命令和操作地址并發往狀態選擇模塊;接收到燒寫信號后,從數據緩存模塊讀取配置碼流,產生的寫命令、操作地址發往狀態選擇模塊,操作數據則直接發往Flash控制器。

3,FPGA配置模塊接收到來自RS232接口模塊的起始地址和重配置信號后,先向待配FPGA器件發送初始化信號,等待初始化完成后向狀態選擇模塊連續發送讀命令和操作地址,并利用從Flash控制器返回的配置碼流來配置FPGA器件。

4,狀態選擇模塊根據外部的燒寫/配置信號選擇Flash控制器的輸入,從而決定控制FPGA目前處于燒寫Flash存儲器狀態還是配置FPGA器件狀態。若為“0”,則輸入燒寫控制模塊產生的命令和地址,控制FPGA處于燒寫Flash存儲器狀態;若為“1”,則輸入配置控制模塊產生的命令和地址,控制FPGA處于配置FPGA器件狀態。

Flash控制器響應這些輸入的命令、操作地址和數據,產生與命令相對應的Flash存儲器控制時序,并返回Flash存儲器的數據輸出。

3.2 性能實際測試

本方案處于編程模式時,系統能夠通過JTAG接口和串口與上位機軟件進行正常的通信,在加載合適的配置文件后,可以完成Flash存儲器的擦除和燒寫操作,實測燒寫速度為160 Kb.需要燒寫多個配置文件時,通過串口工具發送配置文件地址,即可對不同的Flash空間進行操作。

處于配置模式時,以Virtex系列中XCV1000型FPGA為配置對象,其配置文件大小約為5.84 Mb,實測一次配置時間為60 ms,計算得知配置速度約為97 Mb/s,遠大于System ACE解決方案的30 Mb/s.如需切換不同的配置文件,從串口工具發送配置文件地址及重配置信號,即可實現多個配置文件的實時切換。

結語

本文分析了各種傳輸協議接口以及System ACE多配置解決方案的優缺點,根據實際應用需求,提出了一種基于大容量NOR Flash并利用JTAG接口完成配置碼流下載的FPGA多配置系統解決方案。本系統采用Flash存儲器替代配置用PROM或CF卡,節省了硬件成本和空間,且理論上可以支持不限數量的配置文件切換,對FPGA的配置速度也達到了System ACE方案的3倍以上。

fpga相關文章:fpga是什么

存儲器相關文章:存儲器原理

評論