Xilinx FPGA的Fast Startup

高優先級分區的實現

本文引用地址:http://www.czjhyjcfj.com/article/125814.htm為了得到盡可能小的高優先級分區的部分比特流,設計中有一些一般性問題需要考慮。首先,該分區必須只能包含此類組件:或者是時序關鍵組件,或者是系統需要這些組件來執行低優先級部分(如ICAP)的部分重配置。得到小規模初始部分比特流的關鍵是使用盡可能小的區域實現高優先級分區。也就是說,您必須將這個分區局限在FPGA中的一個適當區域中。

為了在FPGA中找到理想的物理位置,這個區域應該提供該設計需要的適當數量的資源。訪問該區域以外的資源也是可行的,但我們不鼓勵這么做——盡管對于I/O引腳來說,

這樣做一般是無法避免的。在尋找適當區域時,還要牢記的是這個FPGA區域有可能會妨礙FPGA設計中非時序關鍵部分的資源。

當您已經對FPGA進行分區,且已經找到了這些分區的適當區域之后,下一步就是使用一個空的(黑盒子)低優先級分區實現高優先級分區。得到的比特流含有很多針對未使用資源的配置幀。您可以刪除這些幀,以便得到針對初步配置高優先級分區的有效部分比特流。[4]

低優先級分區的實現

為了創建低優先級的部分比特流,首先,您要創建含有這兩個分區(即高優先級分區和低優先級分區)的完整FPGA設計的實現。從以前的實現中導入高優先級分區,從而保證其實現方法與原來的實現方法相同。

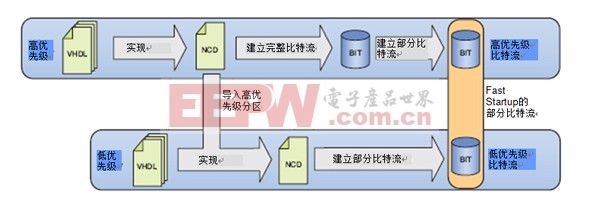

對于Virtex-6器件而言,部分重配置(PR)流程可用于所有上述的實現。這樣,就會自動得到針對低優先級分區的部分比特流。由于Spartan-6器件 系列不支持PR流程,在實現針對Spartan-6設計的Fast Startup時,我們使用了針對差異化的部分重配置的BitGen選項,以獲得低優先級分區的部分比特流。[5]圖3給出了該工具流程的高層概覽。

圖3 – Fast Startup工具流程

實驗與結果

為了在硬件中驗證Fast Startup配置方法,我們的研究小組在一塊Virtex-6 ML605板和一塊Spartan-6 SP605板上實現了這種方法。

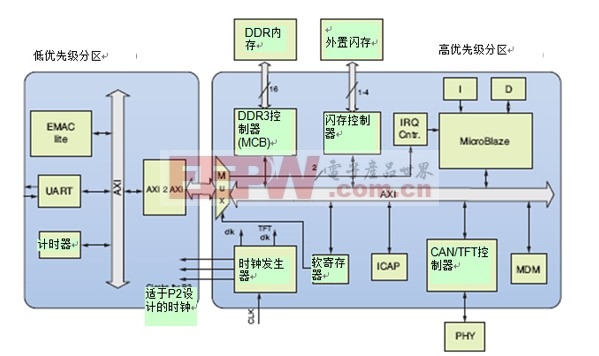

Virtex-6實現的應用背景源自視頻領域。用戶接通視頻系統電源時,他們總是希望立刻就看到系統有所響應,而不用等待數秒。因此,在圖4所示的系統中,一個配備了TFT控制器的高優先級子系統可以迅速點亮TFT屏幕。對于其他低優先級應用,即第二個設計提供了對以太網內核、UART和硬件計時器的控制和訪問。

圖4 – Virtex-6和Spartan-6演示(Virtex-6包括TFT模塊,Spartan-6僅包括CAN模塊)的基本框圖

評論